# PROJET TUTEURE 2001 - 2002

*Rapport technique de réalisation de

maquettes illustrant le transport WCDMA*

# Licence Professionnelle Réseaux et Télécommunications

Patrice ANTONELLI / Emmanuel MANISCALCO

[antoyoda@caramail.com](mailto:antoyoda@caramail.com) / [emaniscalco@free.fr](mailto:emaniscalco@free.fr)

## INTRODUCTION

Cette brochure aidera à la compréhension de la réalisation d'autres plaquettes identiques. Ce document est un rapport de réalisation, l'ensemble des cours se rapportant aux différents sujets abordés sont consultable dans le mémoire « **Réalisation d'une maquette pédagogique illustrant le transport par WCDMA** ».

Le sujet de notre projet est le suivant :

Réalisation d'une maquette pédagogique illustrant le transport par WCDMA. La maquette devra illustrer les mécanismes exploités lors du partage multi-utilisateurs d'un canal unique radiofréquence, par Wireless Code Division Multiple Access. Les caractéristiques seront compatibles avec l'instrumentation du Génie Electrique, dans le domaine des hautes fréquences ( $Z_c = 50\Omega$ ). Outre la maquette, deux documents seront produit : un descriptif technique en vue de production de six exemplaires, et d'un document pédagogique guidant les élèves dans la compréhension des mécanismes WCDMA. »

## PLAN DU RAPPORT

## INTRODUCTION

## PLAN DU RAPPORT

### 1    REALISATION D'UNE MAQUETTE DE TRAVAUX PRATIQUE

#### 1.1    *Introduction*

#### 1.2    *Le Générateur Pseudo-Aléatoire*

#### 1.3    *La corrélation des signaux*

#### 1.4    *La Delay Locked Loop DLL*

#### 1.5    *Schéma complet*

### 2    Réalisation d'une maquette Emetteur en WCDMA

#### 2.1    *Introduction*

#### 2.2    *Génération des différentes horloges*

#### 2.3    *Générateur Pseudo-Aléatoire GPA*

#### 2.4    *Le comparateur 8 bits*

#### 2.5    *Générateur Pseudo-Aléatoire GPA*

#### 2.6    *Schéma complet*

### 3    *Le routage des circuits*

#### 3.1    *introduction*

### 4    *Conclusion*

## 5 **Remerciements**

### 1 REALISATION D'UNE MAQUETTE DE TRAVAUX PRATIQUE

#### 1.1 *Introduction*

Le but de cette partie est la fabrication d'une maquette de Travaux Pratique qui, servira de support pour des élèves de l'IUT. Elle illustrera le fonctionnement d'un Générateur Pseudo Aléatoire, du rôle joué par une corrélation de signaux ainsi que la philosophie d'une DLL.

Seulement le câblage nécessaire au minimum de fonctionnement sera présent au routage final, le reste des liaisons fera l'objet d'e Travaux Pratique, et sera connecter par les élèves.

#### 1.2 *Le Générateur Pseudo-Aléatoire*

Il est utilisé pour créer, des blocs qui seront découpés pour définir les clés

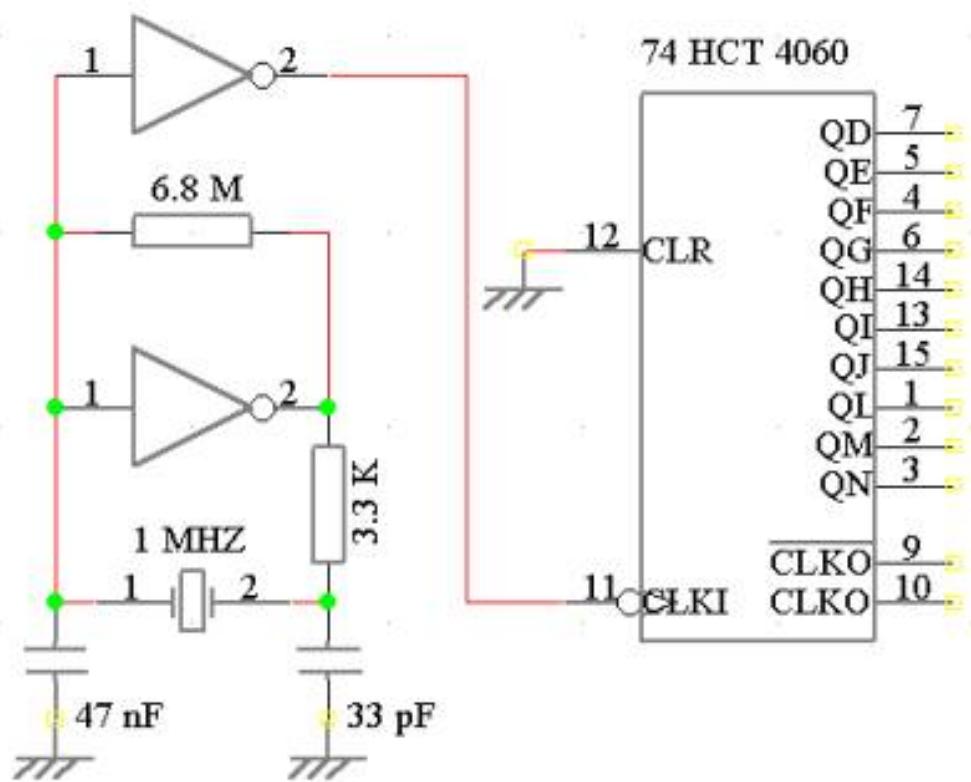

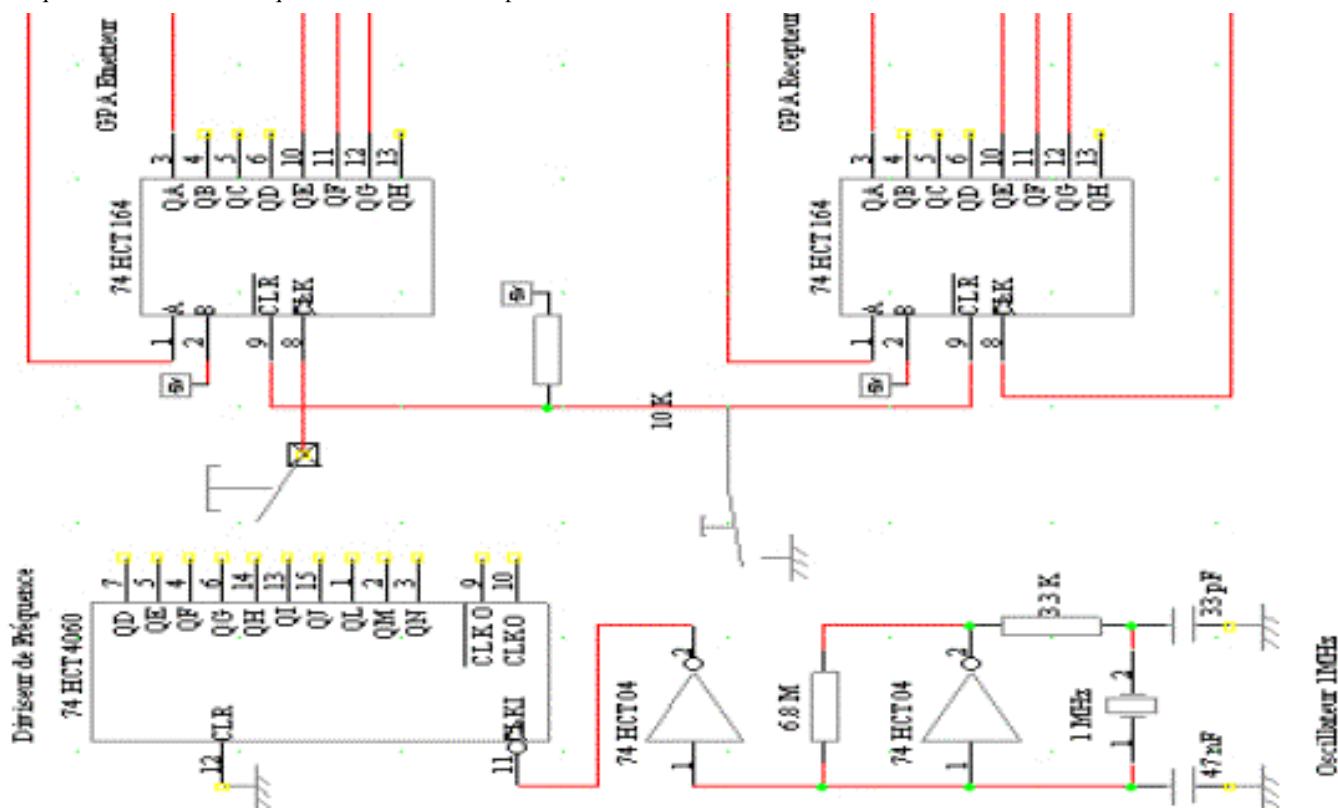

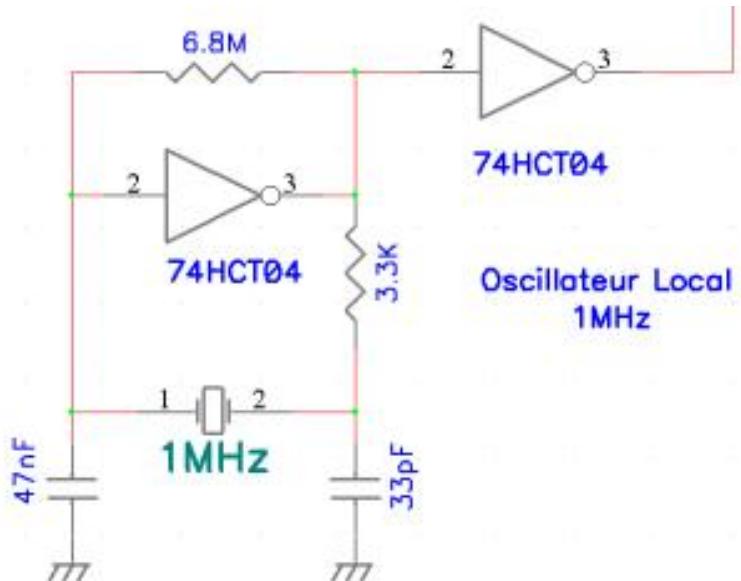

Tout d'abord voici le schéma de l'oscillateur local (de 1MHz), suivit de son diviseur de fréquence qui nous permettront de travailler à des fréquences variant de 1MHz à 1KHz

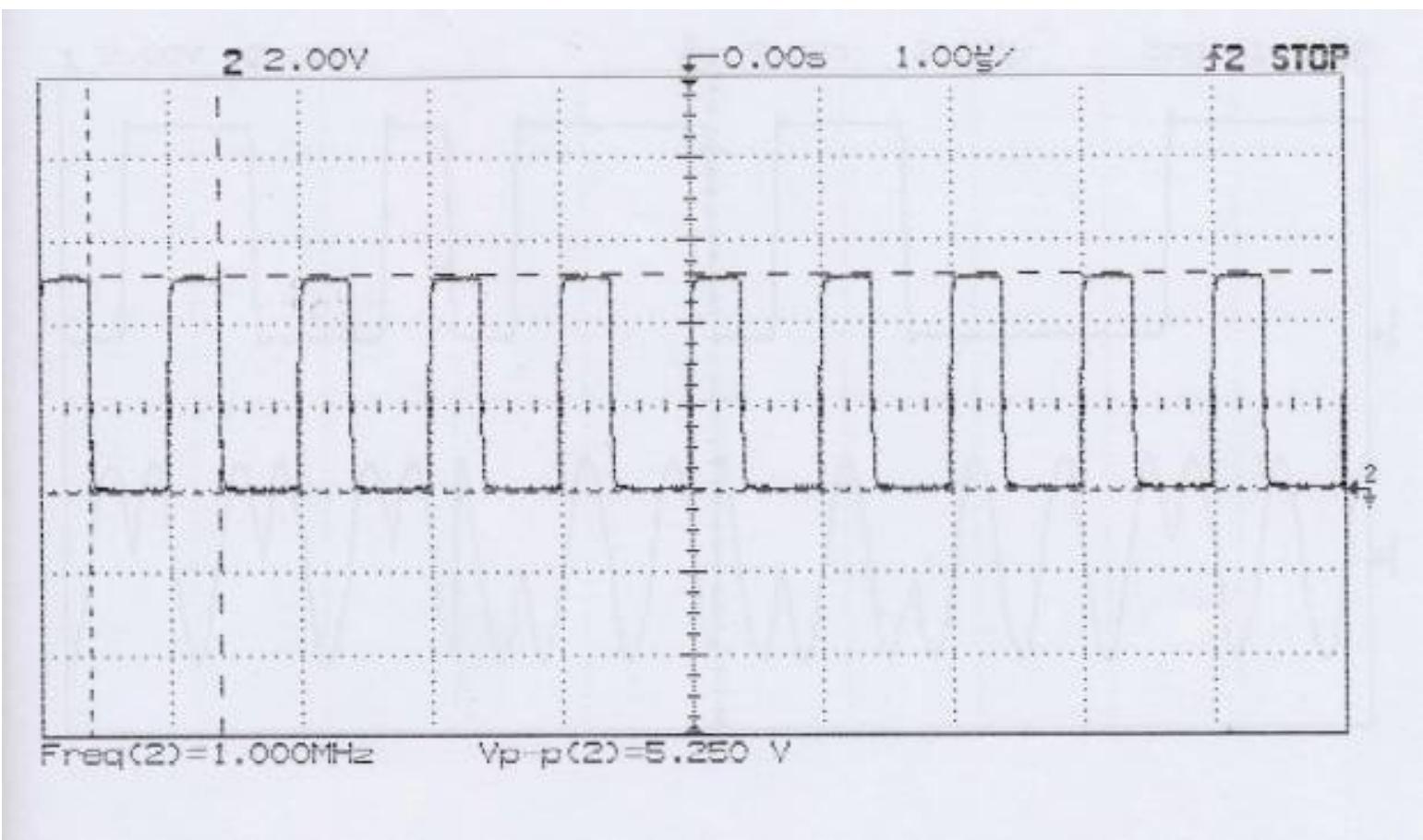

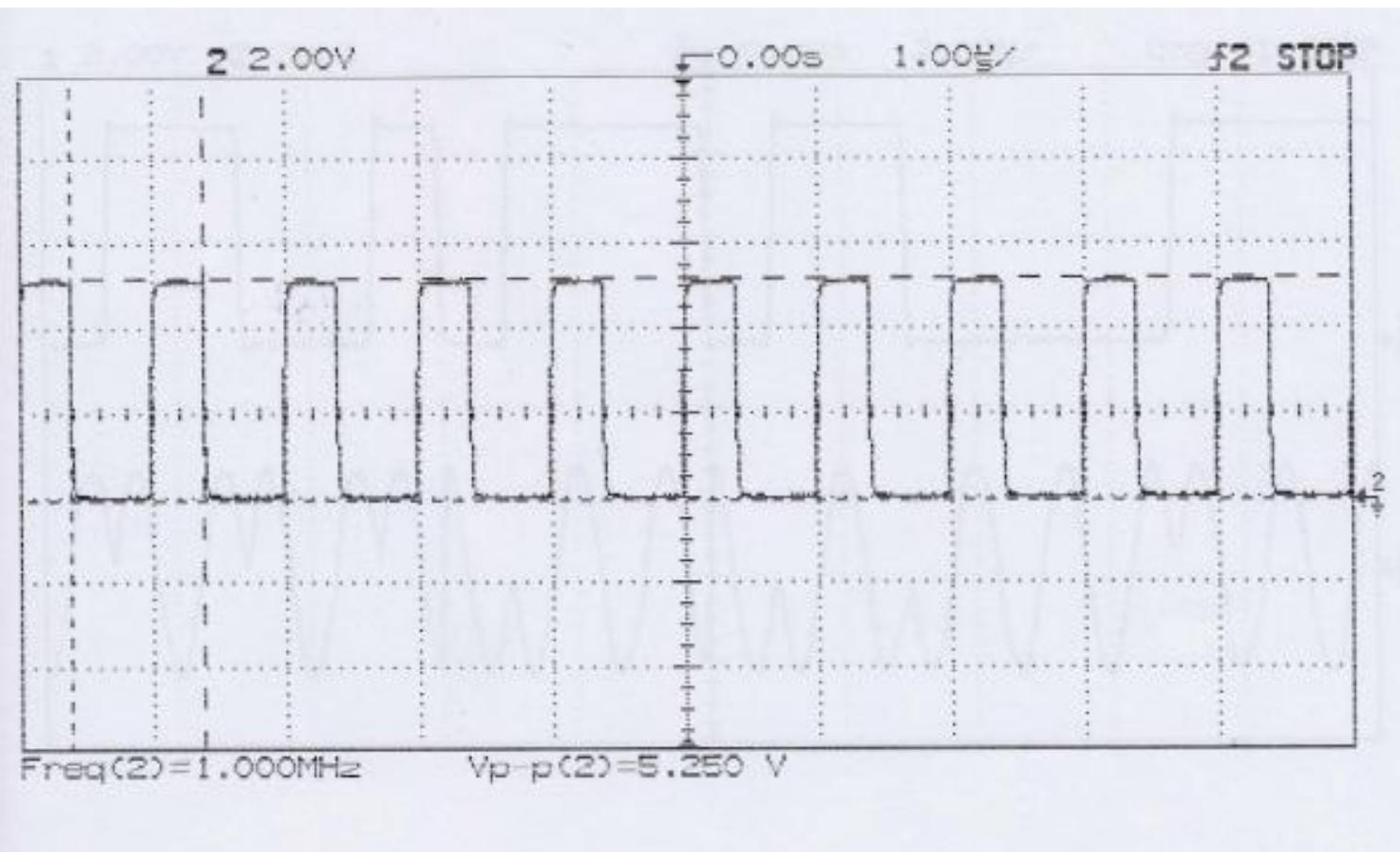

Ce montage nous a permis de faire le relevé du chronogramme suivant, l'horloge est régulière et de fréquence 1Mhz, les différentes subdivisions nous ont donné des graphes semblables pour les diverses fréquences fournies par le compteur binaire (74 HCT 4060).

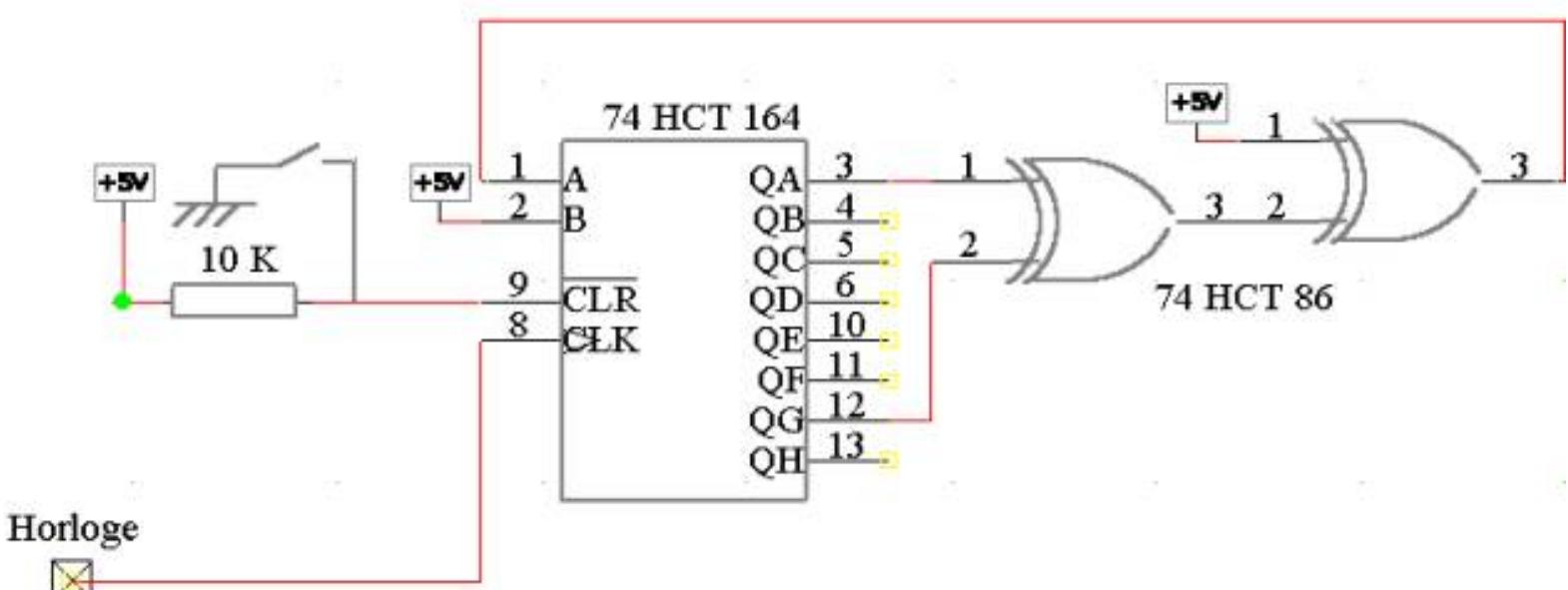

Pour éviter d'avoir des séquences binaires indésirables (11111...1111), nous avons installé un inverseur qui supprimera cette suite. Mais pour des raisons de sécurité il faut tout de même câbler un dispositif de remise à « ZERO » des registres pour prévenir tout blocage du système pendant les diverses manipulations.

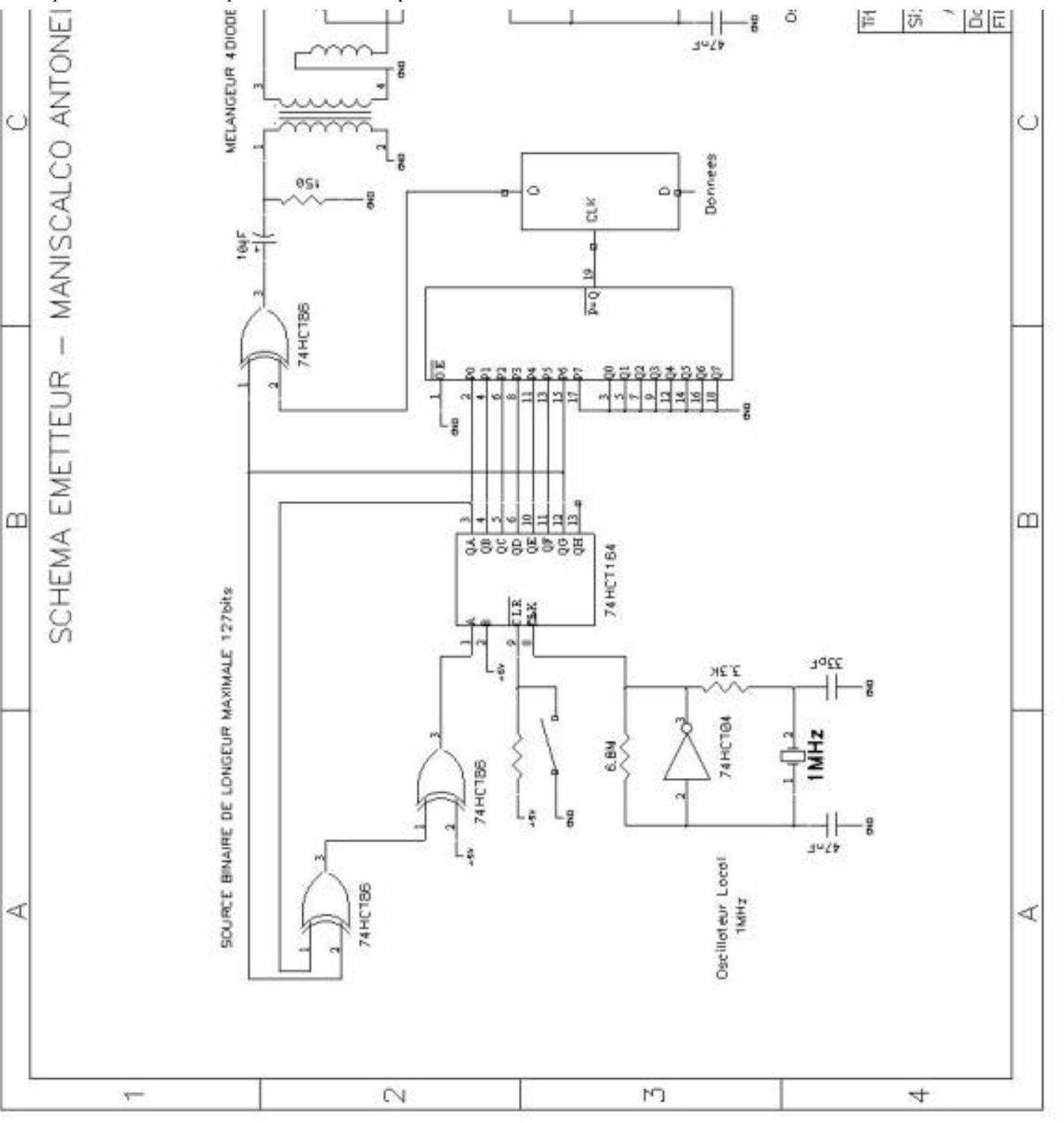

Le schéma de « l'émetteur » suivant prend en compte les mis au point effectué sur le montage :

Le signal d'horloge utilisé pour l'ensemble des tests est  $f = 1\text{MHz}$ , fréquence originale de l'oscillateur.

En Utilisant les combinaisons du tableau suivant, on assure un signal pseudo aléatoire périodique, nécessaire pour la cohérence de la maquette.

| N  | Connexions Possibles pour les GPA de Hamming |      |       |      |      |      |

|----|----------------------------------------------|------|-------|------|------|------|

| 3  | 3⊕2                                          | 3⊕1  |       |      |      |      |

| 4  | 4⊕3                                          | 4⊕1  |       |      |      |      |

| 5  | 5⊕3                                          | 5⊕1  |       |      |      |      |

| 6  | 6⊕5                                          | 6⊕1  |       |      |      |      |

| 7  | 7⊕6                                          | 7⊕1  | 7⊕4   | 7⊕3  |      |      |

| 8  | 8⊕7⊕5⊕3                                      |      |       |      |      |      |

| 9  | 9⊕5                                          | 9⊕4  |       |      |      |      |

| 10 | 10⊕7                                         | 10⊕3 |       |      |      |      |

| 11 | 11⊕9                                         | 11⊕2 |       |      |      |      |

| 12 | 12⊕11⊕8⊕6                                    |      |       |      |      |      |

| 13 | 13⊕10⊕6⊕4                                    |      |       |      |      |      |

| 14 | 14⊕13⊕8⊕4                                    |      |       |      |      |      |

| 15 | 15⊕14                                        | 15⊕1 | 15⊕11 | 15⊕4 | 15⊕8 | 15⊕7 |

| 16 | 16⊕14⊕13⊕11                                  |      |       |      |      |      |

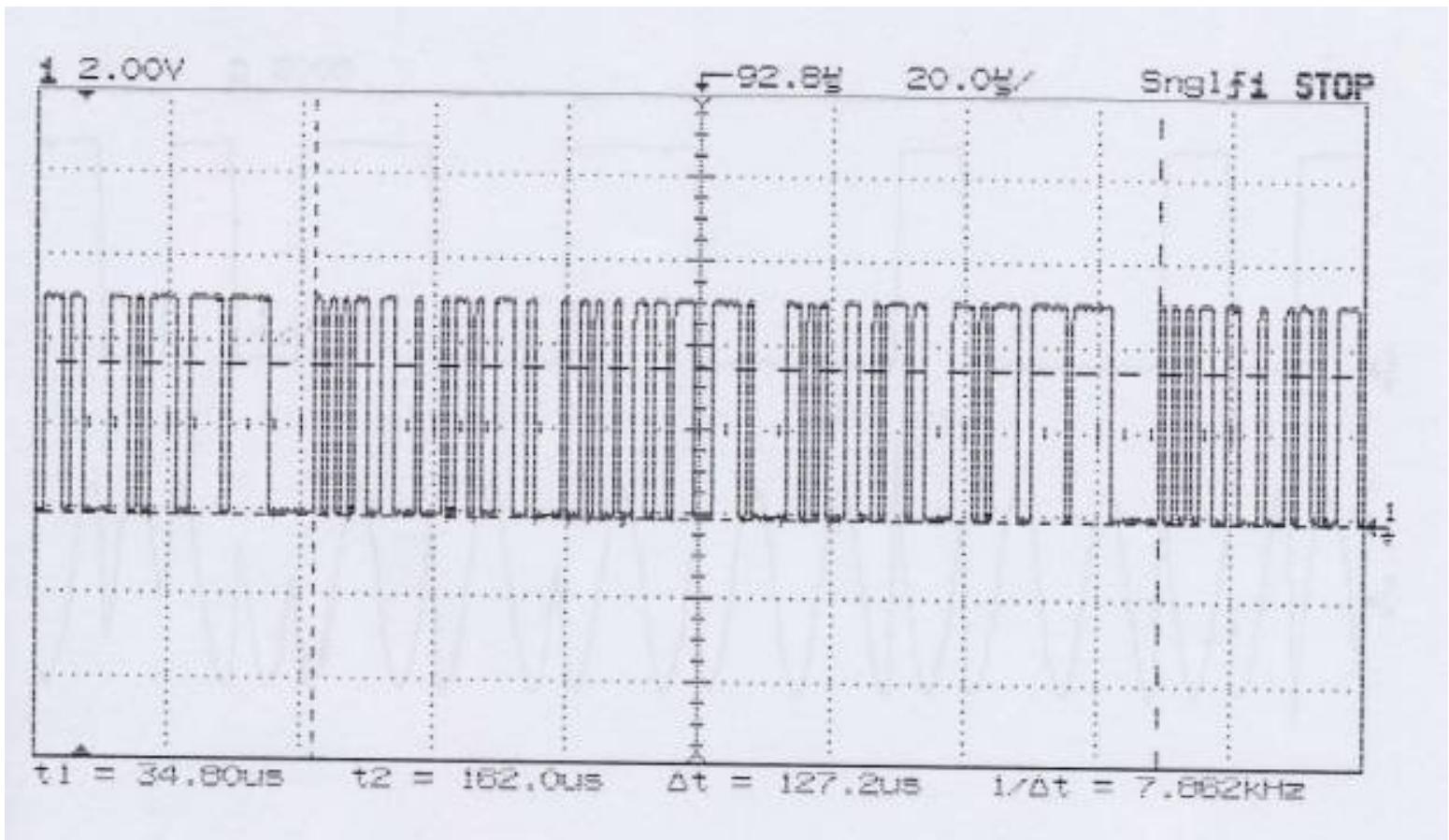

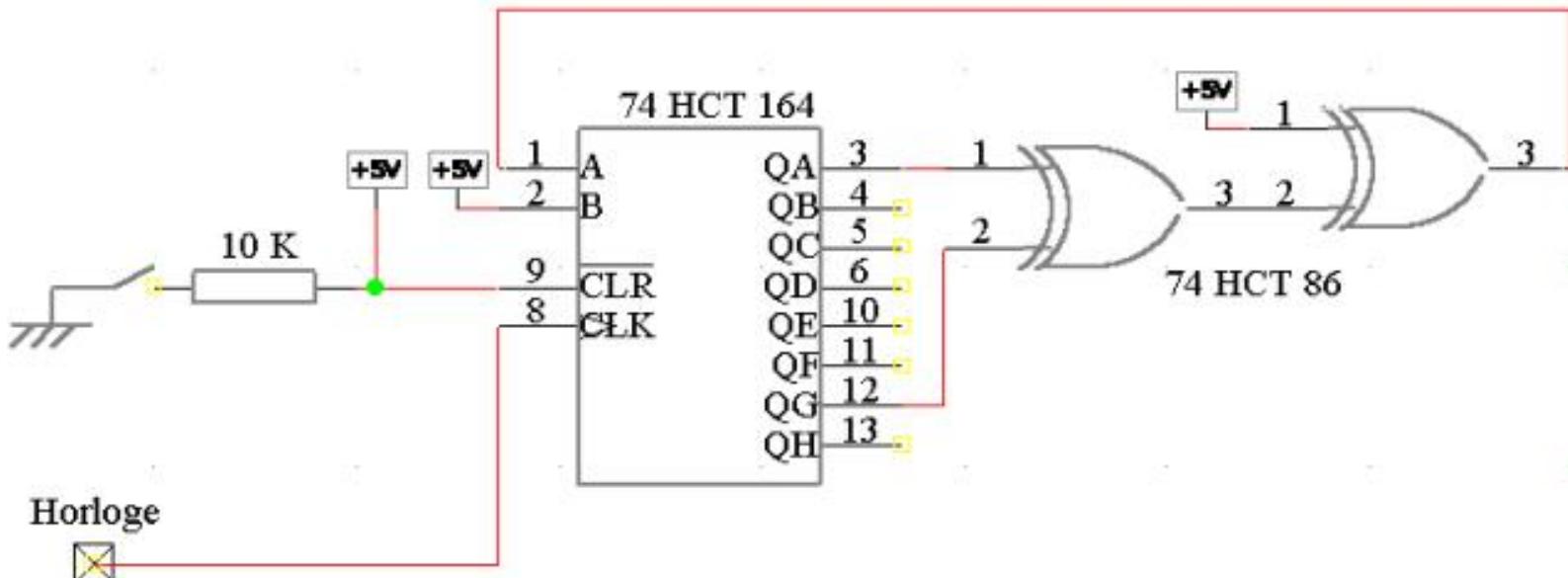

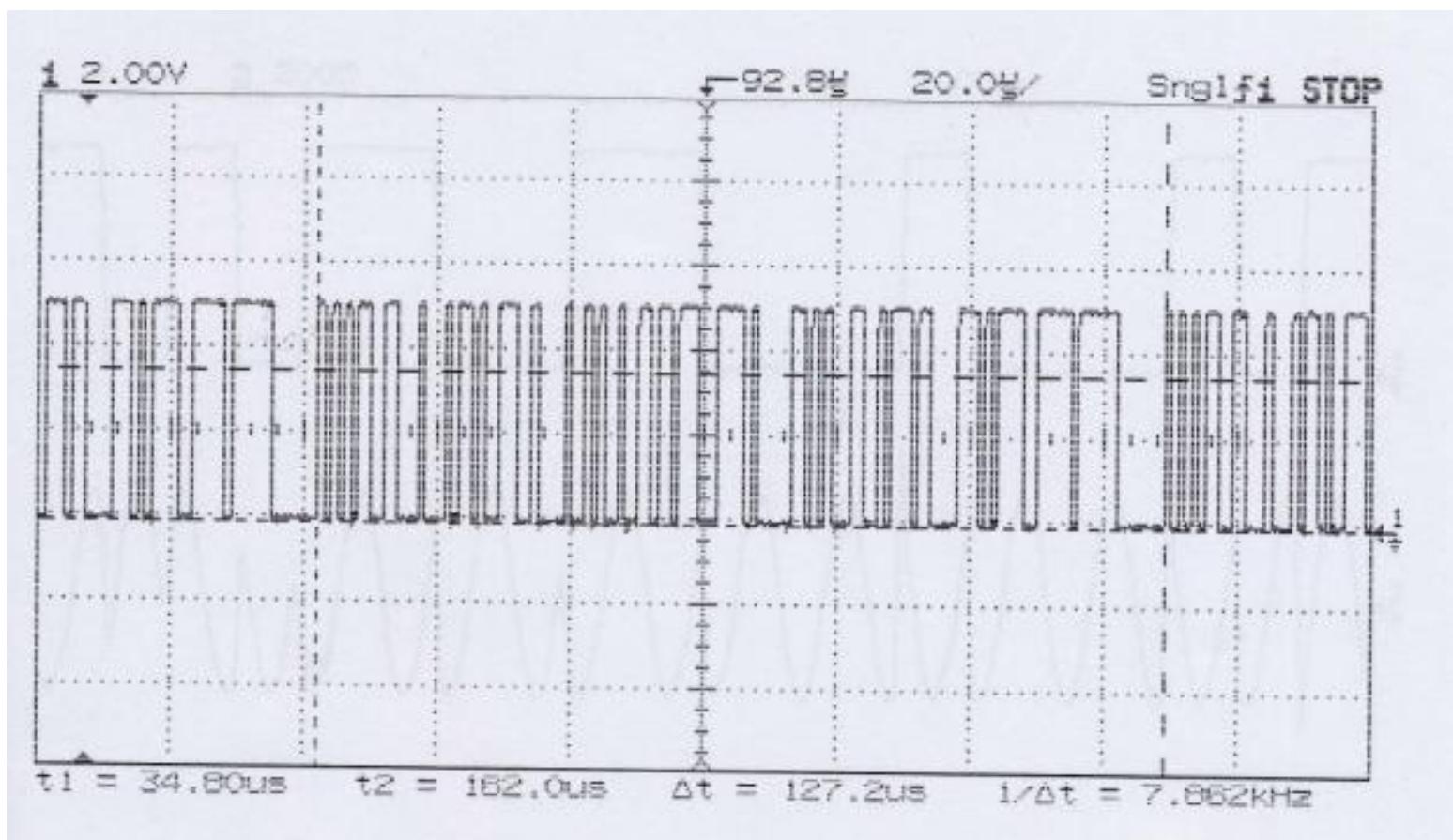

Pour les besoins du projet on traitera le cas issu de la combinaison de  $ak-7$  et  $ak$  soit 8 bits et donc  $(2^n - 1)$  combinaisons avec  $n$  représentant le nombre de bit, dans notre cas on a bien 127 combinaisons. Le chronographe suivant nous présente un période du générateur. On peut y observer les 127 phases pseudo-

aléatoires.

On relève une période  $T = 127\mu s$  Avec un  $T_b = 1\mu s$

### 1.3 La corrélation des signaux

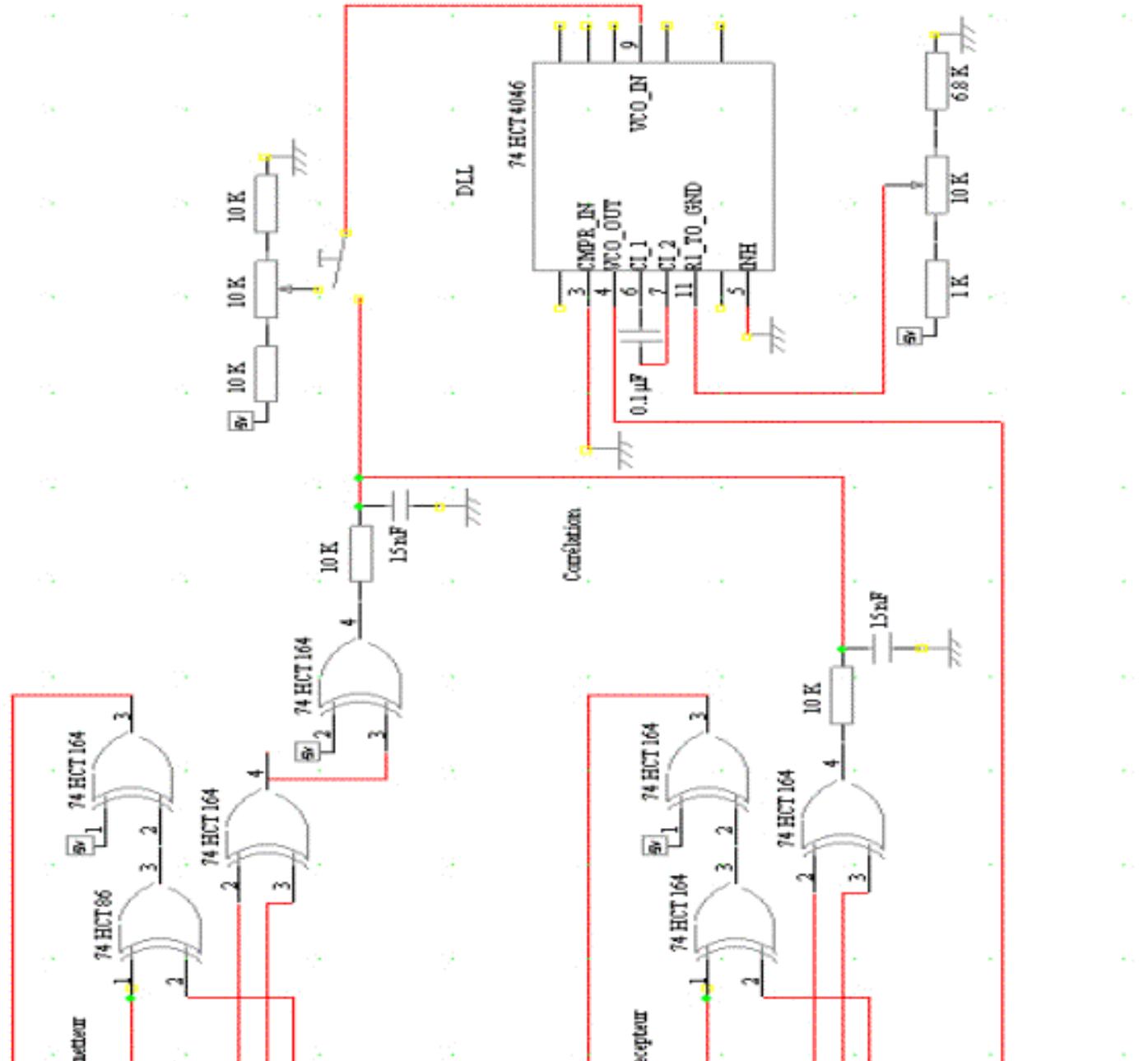

Pour continuer le processus on câble un 2<sup>nd</sup> GPA « le récepteur » calqué sur l'architecture de « l'émetteur » dont les sorties seront numérotées de bk à bk-7. Le système GPA étant bouclé la phase de corrélation commence. En effet notre future DLL sera commandé en tension par la pente formé par la corrélation d'un signal en avance et d'un signal retardé.

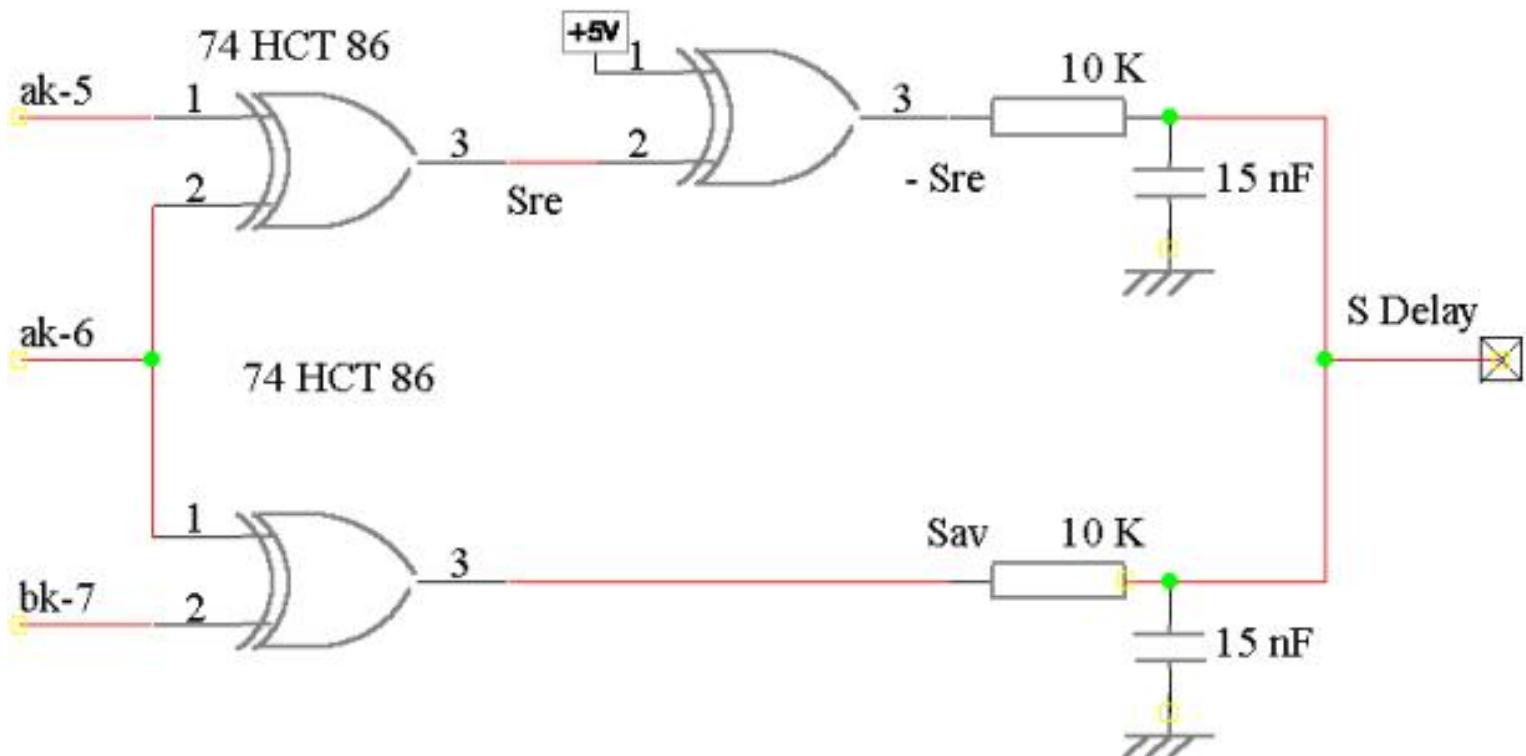

Pour les besoins du test on a utilisé ak-5  $\oplus$  ak-6 et ak-6  $\oplus$  bk-7, signaux nous donnant l'avance et le retard de délai. Et pour faciliter les réglages on alimente les

deux GPA avec la même horloge de 1MHz.

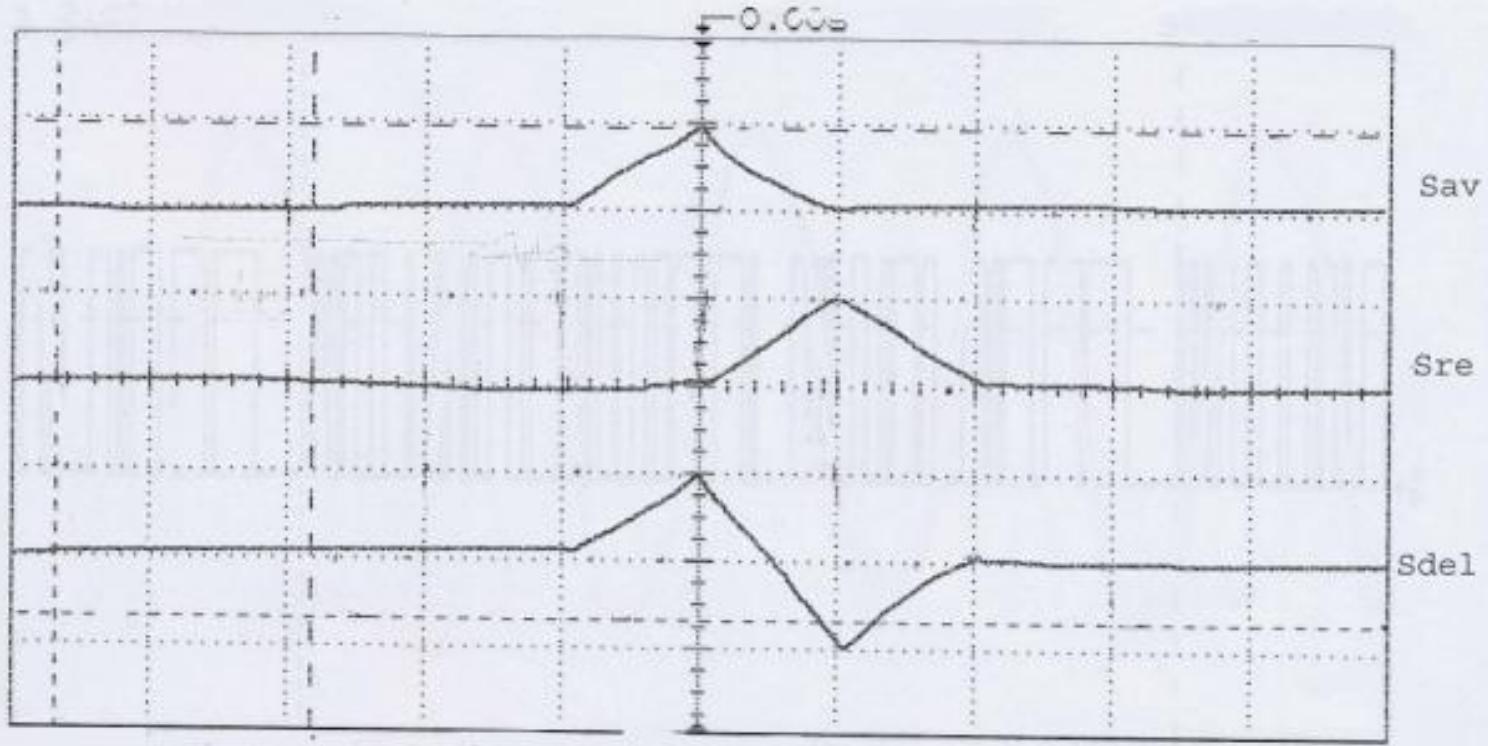

La corrélation revient à avoir une pente relative au décalage en temps entre les 2 signaux, donc à faire  $S_{Delay} = S_{av} - S_{re} = S_{av} + (-S_{re})$ , pour effectuer la soustraction on place un inverseur. Puis avant de faire la somme des courants et donc des signaux on les moyenne à l'aide de filtre RC Passe Bas du 1<sup>er</sup> ordre pour éliminer la composante continue des signaux  $S_{av}$  et  $S_{re}$ .

$$H(p) = \frac{1}{\tau p} = \frac{1}{(RC)p} \text{ avec un } F_c \text{ Fréquence de coupure} = 1\text{KHz}$$

$$F_c = \frac{1}{2\pi RC} \text{ Soit le couple } R=10K\Omega \text{ et } C=15nF$$

schéma de câblage du corrélateur

Ces chronogrammes représentent les signaux  $S_{av}$   $S_{re}$  et  $S_{Delay}$  filtré( sans leur composante continue )

C'est le signal Sdelay qui va commander en tension la DLL, en effet Sdelay est l'image du retard entre les signaux des différents GPA.

#### 1.4 *La Delay Locked Loop DLL*

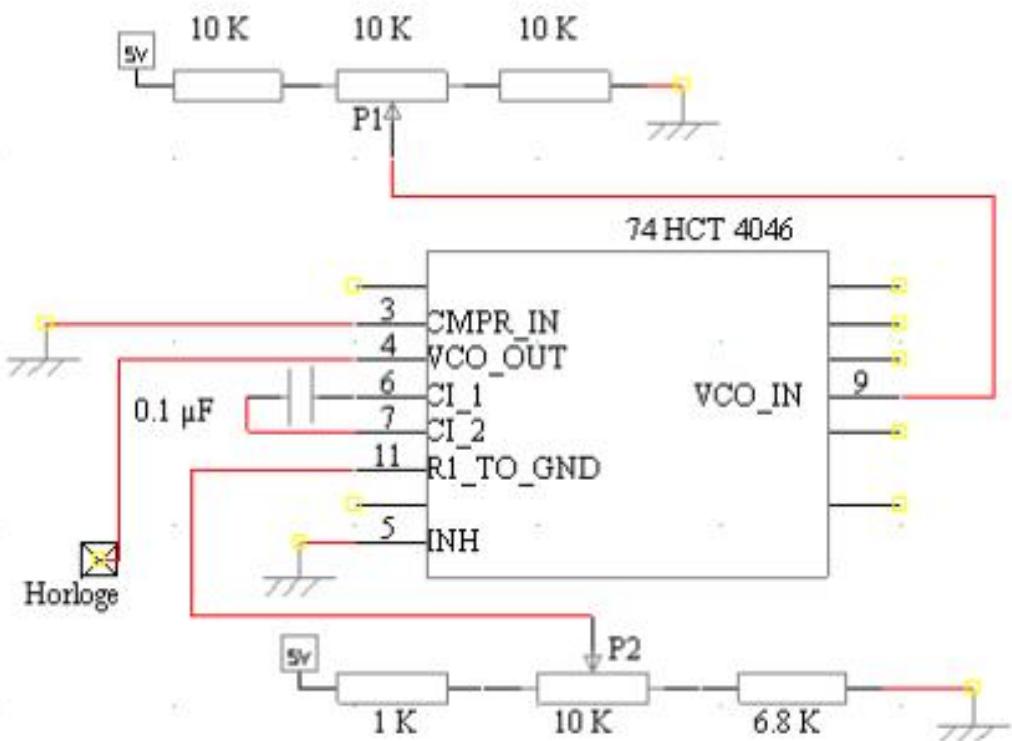

La DLL est commandé en tension grâce à la pente formée par la corrélation précédente. Mais pour faire les réglage de la DLL il faut tout d'abord fixer l'entrée à VCO\_IN=2,5V avec le potentiomètre P1, puis à l'aide de l'abaque « typical values of VCO centre fréquence » (voir doc. technique) on choisit les composant assurant la fréquence, ici 1MHz.

Le couple  $C=0.1\mu F$  et  $R=10k\Omega$  est le plus proche des données constructeur mais pour laisser une marge de réglage sur la fréquence on introduira le potentiomètre P2 qui fera varier l'impédance de  $6.8k\Omega < R < 16.8k\Omega$ .

Le schéma si dessous correspond au câblage de test de la DLL.

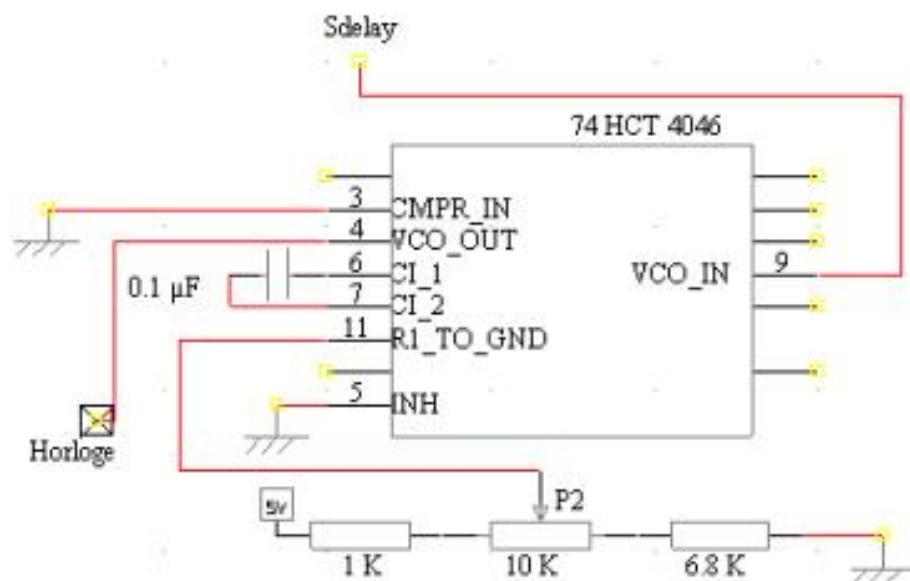

La fréquence étant maintenant réglée à 1Mhz on peut remplacer le potentiomètre P1 par le signal Sdelay.

Le schéma suivant est maintenant en place :

Le teste final est de bouclé le DLL sur l'entrée d'horloge du GPA « récepteur », on peu constater que les signaux issus des deux GPA sont en phase

et reste stable de  $F_{ol} - \frac{1}{Tb}$  à  $F_{ol} + \frac{1}{Tb}$  soit de  $1.10^{3-} \frac{1}{127.10^{-6}}$  à  $1.10^{3+} \frac{1}{127.10^{-6}}$

AN :  $992.2\text{KHz} < F_{stable} < 1007.78\text{KHz}$  calculé pour une fréquence centrale de 1MHz

est un GPA de 7Bits

La boucle est stable, la plaquette est maintenant reste à faire le routage grâce au logiciel Ares. L'ensemble des schémas est dans la partie routage du rapport.

## 1.5 Schéma complet

## 2 Réalisation d'une maquette Emetteur en WCDMA

### 2.1 *Introduction*

Cette partie va présenter le côté émission du projet avec les différents éléments qui le compose : les oscillateurs, le GPA, le multiplicateur, le comparateur et le mélangeur.

### 2.2 *Génération des différentes horloges*

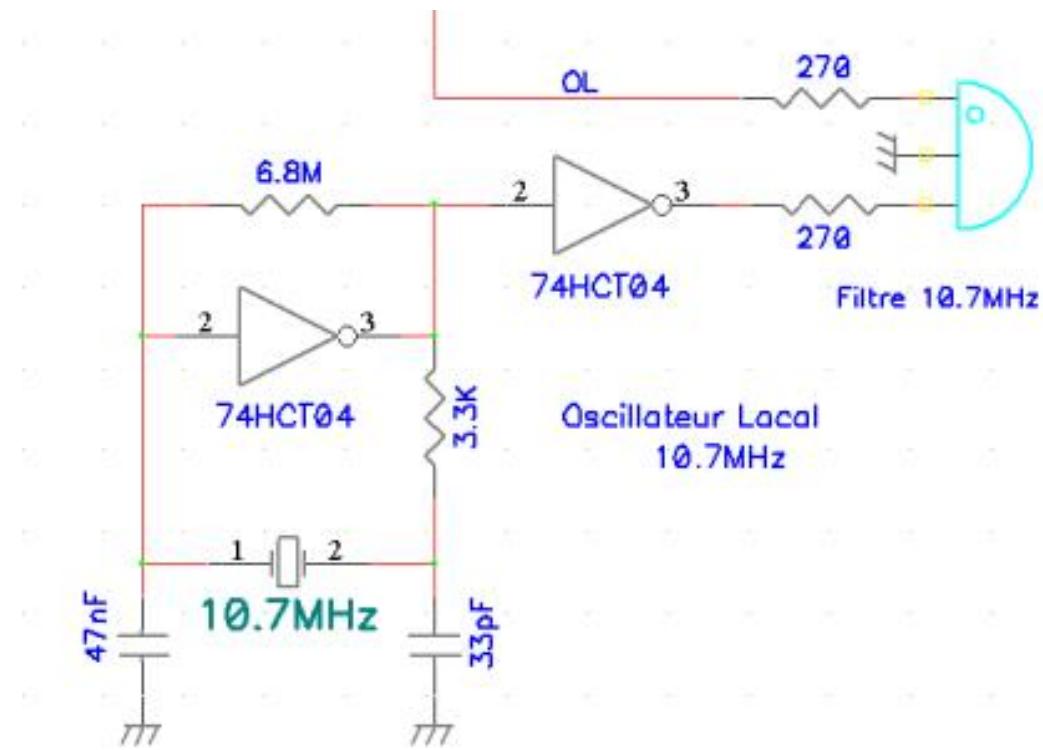

Avant tout la création de deux horloges, une carré de fréquence 1 MHz pour fixer le débit du GPA, et une sinusoïdale de fréquence 10.7MHz pour alimenter notre mélangeur, est nécessaire pour cadencer l'ensemble de la maquette ; Afin d'être autonome.

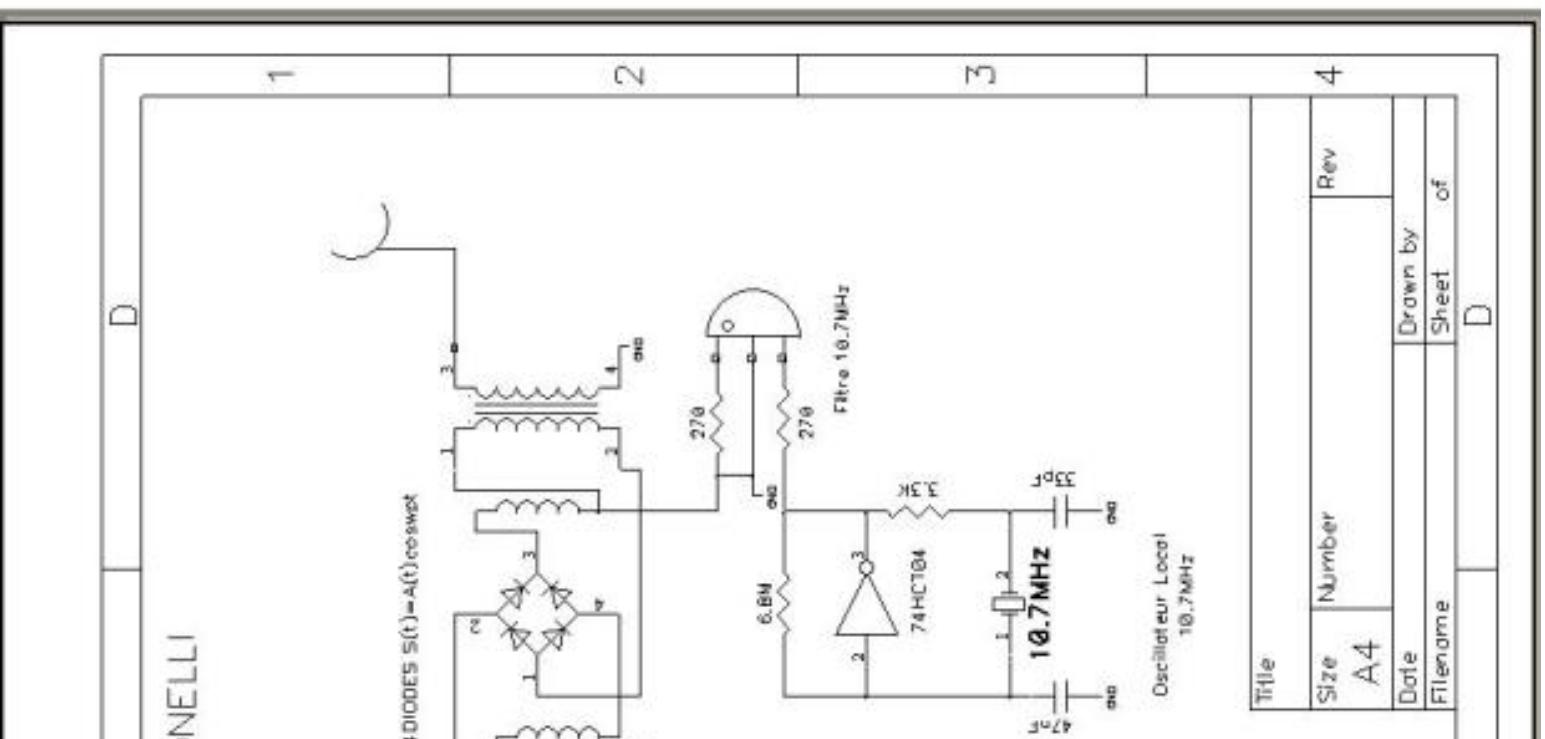

Ci-dessous le schéma de l'oscillateur local à signal carré.

Le chronogramme suivant représente le relevé du signal d'horloge générée grâce au câblage précédent :

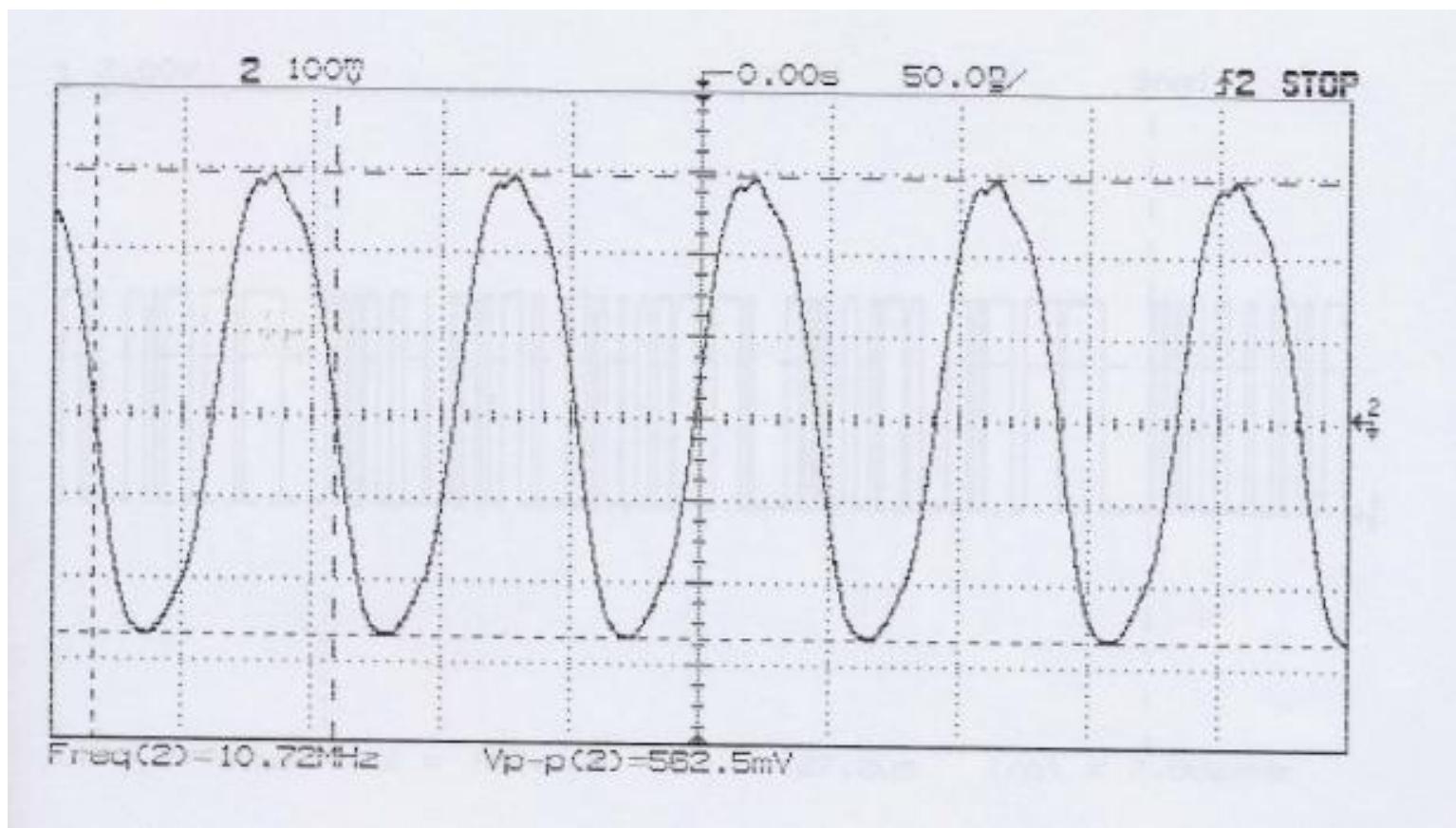

Le schéma synoptique de l'oscillateur à signal sinusoïdal de fréquence 10,7MHz se compose d'un générateur de carré, suivi d'un filtre sélectif qui choisit uniquement la fréquence de 10,7MHz transformant le signal carré en sinus.

Le tracé de ces graphes a été réalisé en charges, on a bien une sinusoïde rythmé à 10,7 Mhz et de valeur crête à crête  $V_{pp} = 562.5\text{mV}$  suffisant pour déclencher les diodes du mélangeur.

### 2.3 Générateur Pseudo-Aléatoire GPA

Le schéma de « l'émetteur » suivant est semblable à celui développé en première partie du rapport.

Les chronogrammes sont identiques a ceux précédemment relevé :

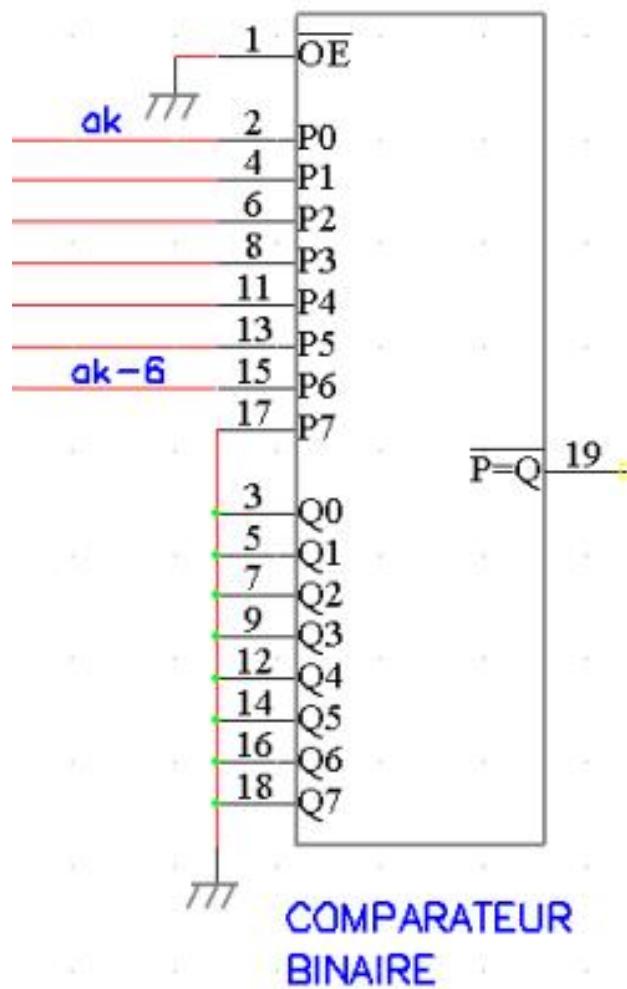

## 2.4 Le comparateur 8 bits

## Envoie des données à la fréquence F= 8kHz

Afin d'envoyer les données à cette fréquence, il faut diviser le débit du GPA (1MHz) par 127. soit :

$$F_{comp} = \frac{F_{OL}}{127} \approx 8KHz$$

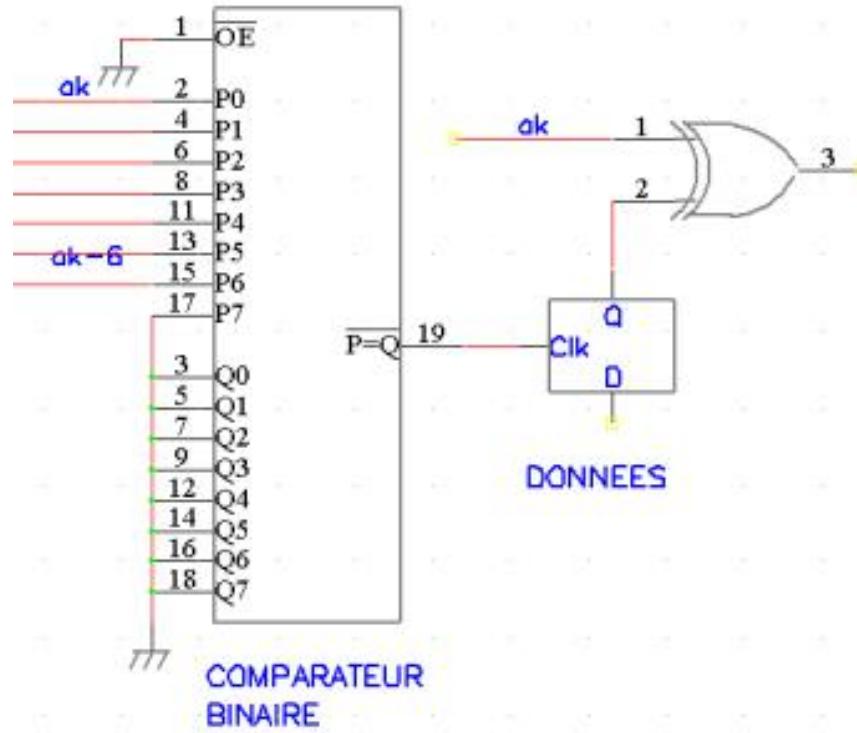

Le GPA fonctionne avec 127 combinaisons unique et périodique, il suffit donc de créer une détection de séquence grâce à un comparateur 8 bits (74 HCT 688) qui comparera le signal issu du GPA avec une combinaison choisit dans l'ensemble des 127 séquences.

Schéma de câblage

Cette nouvelle horloge commandera une bascule D (74 HCT 75) qui sera, grâce à un OUEX (74 HCT 86), multiplier par le code résultant du GPA. Pour réaliser l'étalement de spectre.

## Schéma synoptique du montage de multiplication :

### 2.5 Générateur Pseudo-Aléatoire GPA

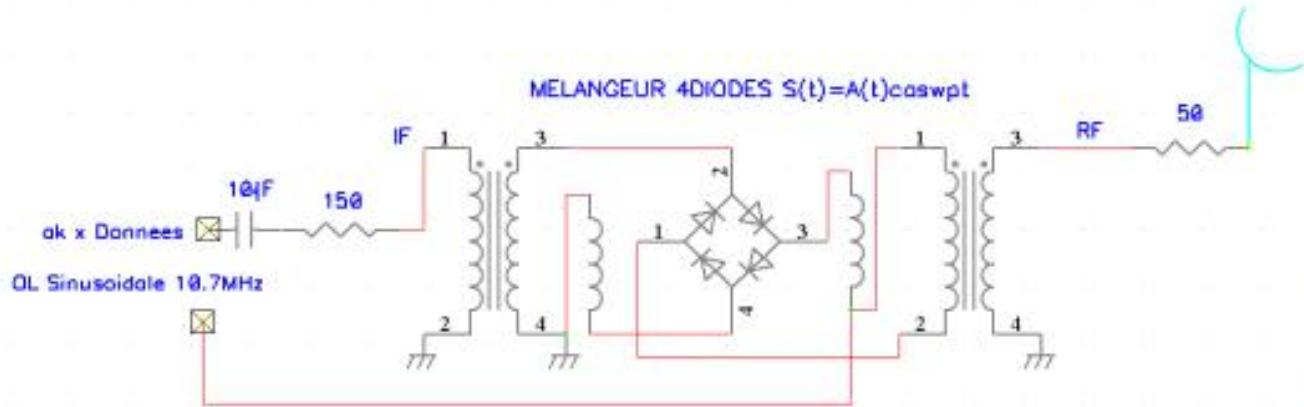

La modulation sera utilisée pour transposer le signal émis au canal de transmission, pour cela nous utilisons un mélangeur à diodes schottky SCM 1, Ce mélangeur est le plus souvent constitué de 4 diodes montées en anneau et de deux transformateurs permettant d'attaquer les diodes de façon convenable, qui brassera la porteuse issue de notre Oscillateur sinusoïdale, avec la multiplication de nos données avec le signal sortant du GPA filtré pour supprimer la composante continue, pour éviter des problèmes de niveau d'injection sur l'entrée du mélangeur.

$$H(p) = \frac{1}{\tau p} = \frac{1}{(RC)p} \text{ avec un } F_c \text{ Fréquence de coupure} = 100\text{Hz}$$

$$F_c = \frac{1}{2\pi RC} \text{ Soit le couple } R=150\Omega \text{ et } C=10\mu\text{F}$$

Cette opération nous impose le schéma suivant :

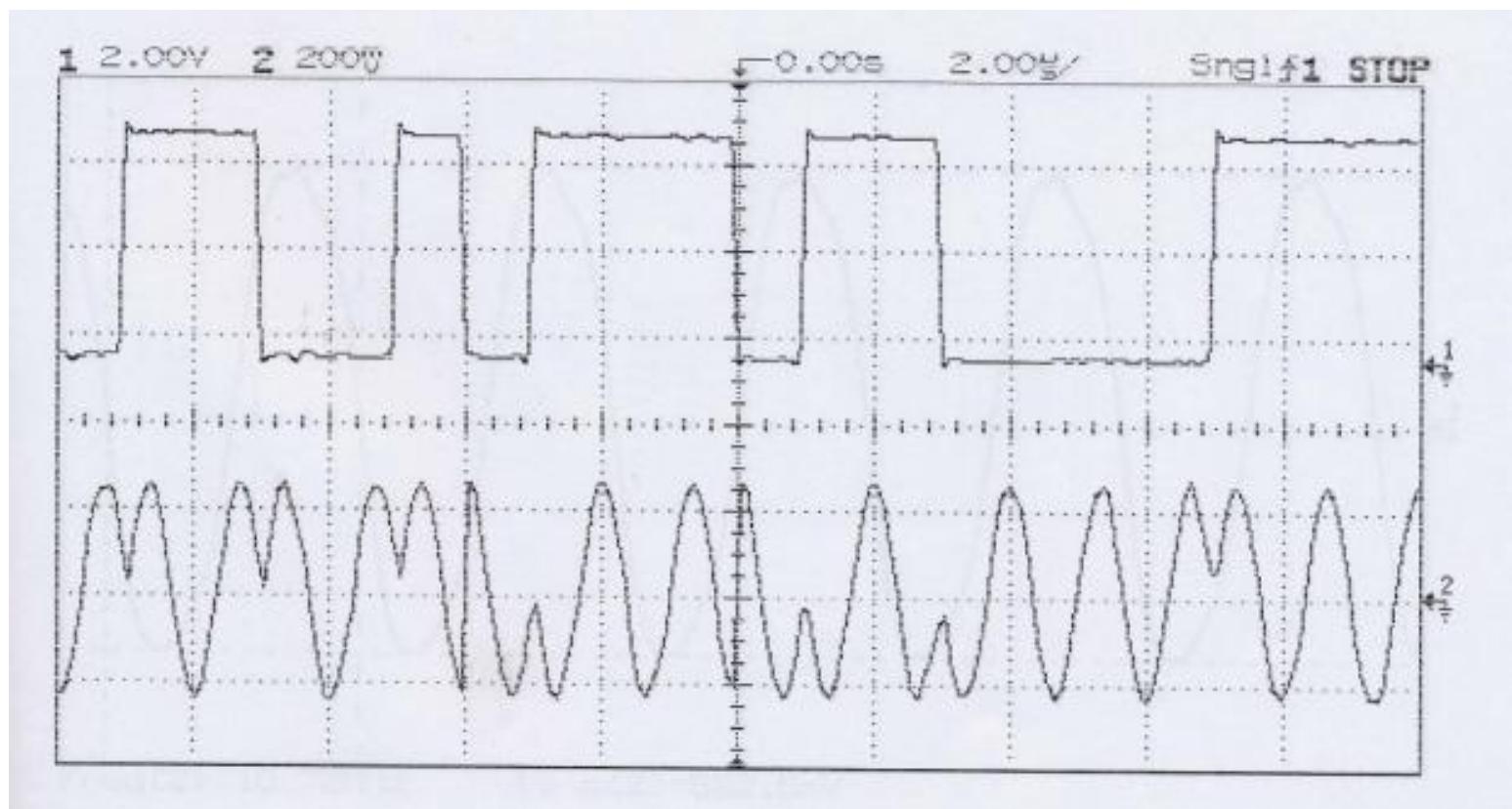

voici donc les chronogrammes du GPA et de la sortie du modulateur :

Normalement nous devrions observer 10 périodes de la porteuse dans un bit du GPA mais l'oscilloscope étant limité cette mesure a été effectuée avec un seul balayage d'écran, le graphe ne relate pas les vrais signaux mais il donne un aperçut du résultat.

Une étude en fréquence a aussi été réalisée : ce graphe représente fidèlement la modulation utilisée la modulation de phase MDP-2 sur porteuse.

On peu remarquer que le marqueur pointe sur 9.72MHz soit  $F_p - \frac{1}{T_b}$  10.7-1 = 9.7MHz.

## 2.6 Schéma complet

### 3 Le routage des circuits

#### 3.1 *introduction*

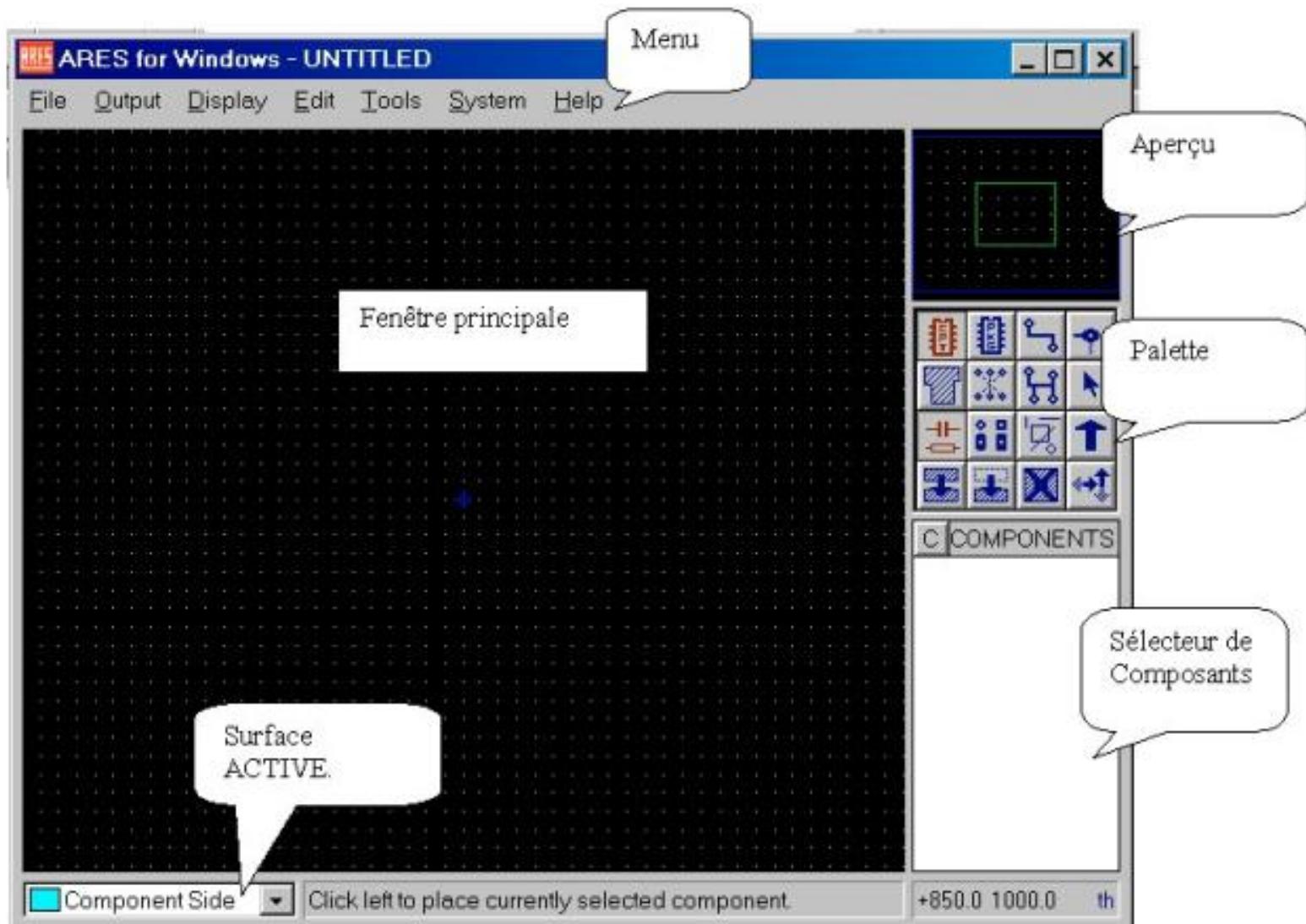

ARES est un logiciel permettant le routage de cartes électroniques en mode

## automatique ou manuel.

Il est possible d'utiliser ARES sans avoir au préalable créé de schéma dans ISIS. Cette fonctionnalité permet de réaliser très rapidement des circuits de faible complexité en plaçant les composants et traçant les pistes directement dans ARES. Une fois les connexions établies il est possible d'effectuer un routage automatique des pistes. Dans ce logiciel vous pouvez également créer de nouveaux boîtiers et les placer dans une bibliothèque.

Une impression d'écran du logiciel Ares

## 4 Conclusion

Les deux parties de notre projet ont été l'application de l'enseignement dispensé au cours de l'année écoulée.

**Nous avons été ravis de pouvoir mettre notre savoir théorique en pratique.**

**Nous avons eu la chance de voir nos objectifs atteints et de savoir que le travail que nous avons entrepris sera suivi d'effets par mes collègues du Service Technique, et peut être par des élèves qui continueront notre projet.**

## **5 Remerciements**

Ce projet n'aurait pas pu être concrétisé sans l'aide de M J.M Mathieu notre professeur tuteur et sans la collaboration des techniciens, qui nous ont fourni l'ensemble du matériel nécessaire à la création de notre projet mais aussi nous ont accordé de leur temps pour des formations sur les différents logiciels utilisé et sur des techniques de réalisation qui nous ont aidé à mener à bien notre mission.

Nous les remercions tous pour leur soutien capital dans le déroulement du projet