**Projet Tuteuré :**

**Carte didactique montrant les applications**

**de la corrélation de séquences binaires.**

Tuteur de projet : J-M Mathieu

Pos tenu compte

de mes modifs.

## Remerciement

Nous tenons tout particulièrement à remercier **M.Mathieu**, notre tuteur de projet, pour son aide et pour le temps qu'il nous a accordé durant ces douze semaines.

**GONNET Gregory**

**BROSSE Sylvain**

# SOMMAIRE

! confusion entre CDMA et technique d'établissement !

|                                                                        |    |

|------------------------------------------------------------------------|----|

| <b>Introduction</b>                                                    | 3  |

| <b>1) Introduction et principe du CDMA</b>                             | 4  |

| <b>1.1) Introduction du CDMA</b>                                       | 4  |

| 1.1.1) Conditions imposées pour la réalisation du projet               | 4  |

| 1.1.2) Synoptique d'une liaison CDMA                                   | 4  |

| <b>1.2) Principe du CDMA</b>                                           | 5  |

| <b>2) Essais et matérialisation des fonctions</b>                      | 10 |

| <b>2.1) Séquenceurs fournissant les SBLM</b>                           | 12 |

| 2.1.1) Explication d'une SBLM et schéma de principe                    | 12 |

| 2.1.2) Rôle et schéma électrique                                       | 13 |

| <b>2.2) Corrélateur</b>                                                | 15 |

| 2.2.1) Explication et schéma de principe                               | 15 |

| 2.2.2) Rôle et schéma électrique                                       | 16 |

| <b>2.3) Horloge maître et esclave</b>                                  | 18 |

| 2.3.1) Horloge « maître »                                              | 18 |

| 2.3.2) Horloge « esclave »                                             | 19 |

| <b>2.4) Mise en place d'une porteuse (canal)</b>                       | 20 |

| 2.4.1) Rôle                                                            | 20 |

| 2.4.2) Schéma électrique                                               | 20 |

| <b>2.5) Mise en place du brassage et du dé brassage de la porteuse</b> | 21 |

| 2.5.1) Porteuse brassée                                                | 21 |

| 2.5.2) Porteuse dé brassée                                             | 23 |

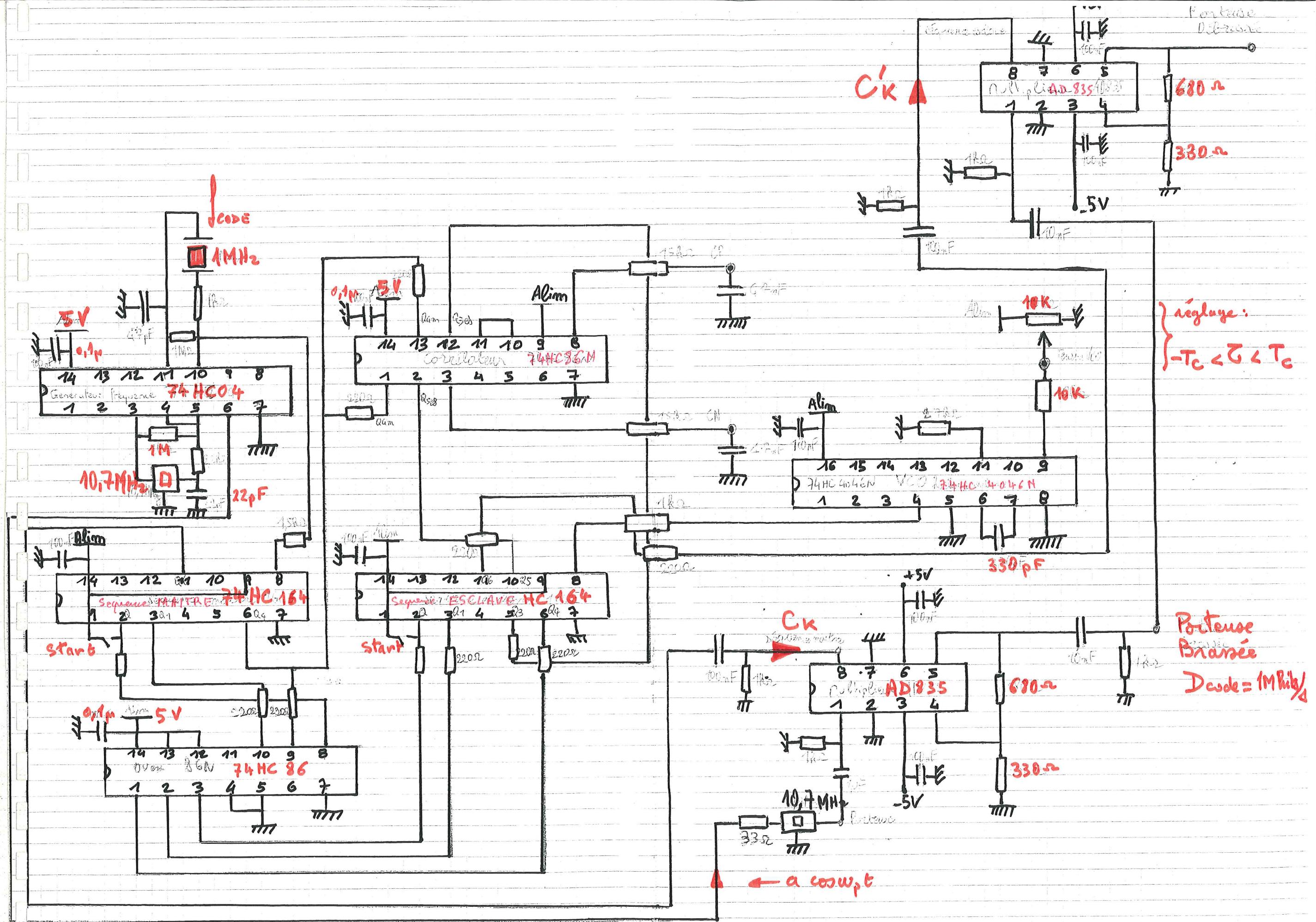

| <b>3) Schéma final de la carte didactique</b>                          | 26 |

| <b>Conclusion</b>                                                      | 28 |

| <b>Annexes</b>                                                         | 29 |

# INTRODUCTION

Ce projet a pour principe de montrer la corrélation de séquences binaires et le mécanisme de dé brassage de porteuse au travers d'une carte didactique.

Notre principe de base est d'envoyer une séquence binaire aléatoire. Elle sera remplacée par une séquence-code qui aura pour fonction de transmettre cette séquence binaire. A la fin de la transmission ce signal sera décodé pour retrouver la séquence binaire envoyée. De ce fait, nous avons pu établir la circulation de l'information avec la technique de multiplexage par Accès Multiple à Répartition par Code (CDMA) à l'aide d'une porteuse. Ce procédé permet de transporter les informations codées dans un canal et ensuite de récupérer la porteuse avec toute son énergie spectrale.

Pour cela quels sont les moyens à mettre en œuvre pour réaliser ce système ?

Dans un premier temps, nous allons expliquer le principe et le rôle du mode de transmission CDMA, puis nous allons aborder la synoptique de la carte didactique avec ses différents composants.

# 1) – Introduction et principe de fonctionnement du CDMA

## 1.1) - Introduction au CDMA

### 1.1.1) Conditions imposées pour la réalisation du projet

Pour effectuer notre projet concernant la corrélation de séquences binaires sur une carte didactique, nous avons du suivre différentes directives imposées par le cahier des charges :

- transmettre des données binaires codées par une séquence code dans un canal de transmission avec un débit de 1Mbits

- utiliser une transmission du type CDMA avec une fréquence de porteuse de 10.7Mhz

- mettre en évidence l'intérêt de cette transmission (étalement de spectre, récupération de la porteuse)

- réaliser une version mono carte

- Fréquence du quartz pour l'horloge maître : 1 MHz

- Fréquence de la porteuse : 10.7 MHz

- Débit binaire :  $D_b = 1 \text{ Mbit}$

- Temps chip :  $T_c = T_b = 1\mu\text{s}$

### 1.1.2) Synoptique d'une liaison CDMA

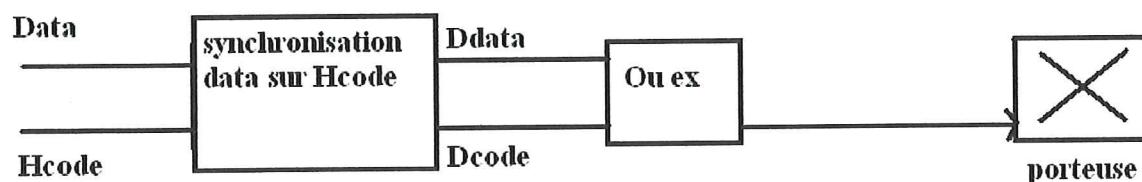

Emission

Arrivée:

## 1.2) - Principe du CDMA

Nous savons qu'il existe plusieurs méthodes de partage d'un support physique ou fréquentiel pour transmettre des informations, exemple :

- FDMA (modulation sur porteuse)

- TDMA (répartition par tranches de temps)

- CDMA (code division multiple access)

- WDMA : Accès multiple par répartition en longueur d'onde : Communications par fibre optique.

Le CDMA est une technique de multiplexage de signaux analogique en bande de base ou sur onde porteuse. Elle est basée sur le principe de l'étalement de spectre et sur des propriétés algébriques de certaines suites binaires appelées codes.

Le CDMA permet une optimisation de la bande, une bonne immunité au bruit et un partage des ressources faciles à gérer par logiciel. Les avantages du CDMA : protection (sécurité) des communications, qualité, faible consommation, flexibilité de l'allocation.

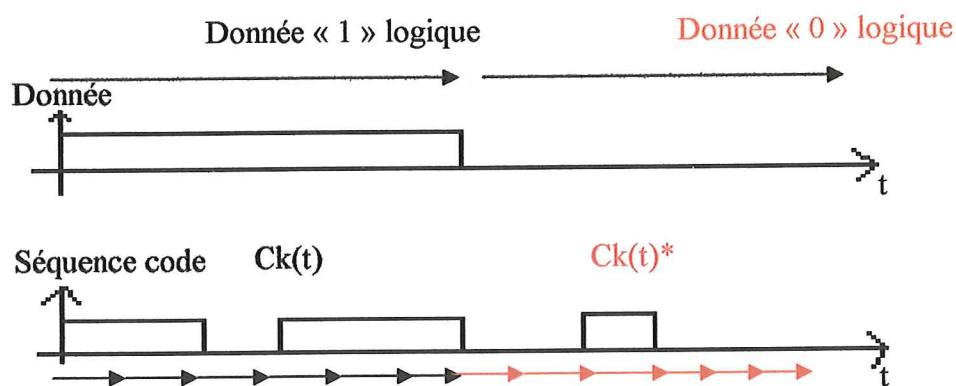

Le principe consiste à remplacer un « 1 » logique par une séquence code  $C_k(t)$  constitué de  $M$  « codes » et chaque bit « 0 » par la séquence complémentaire  $C_k(t)^*$ .

Dans l'exemple, il faut 6 chips, pour représenter un « 1 » logique ou un « 0 ».

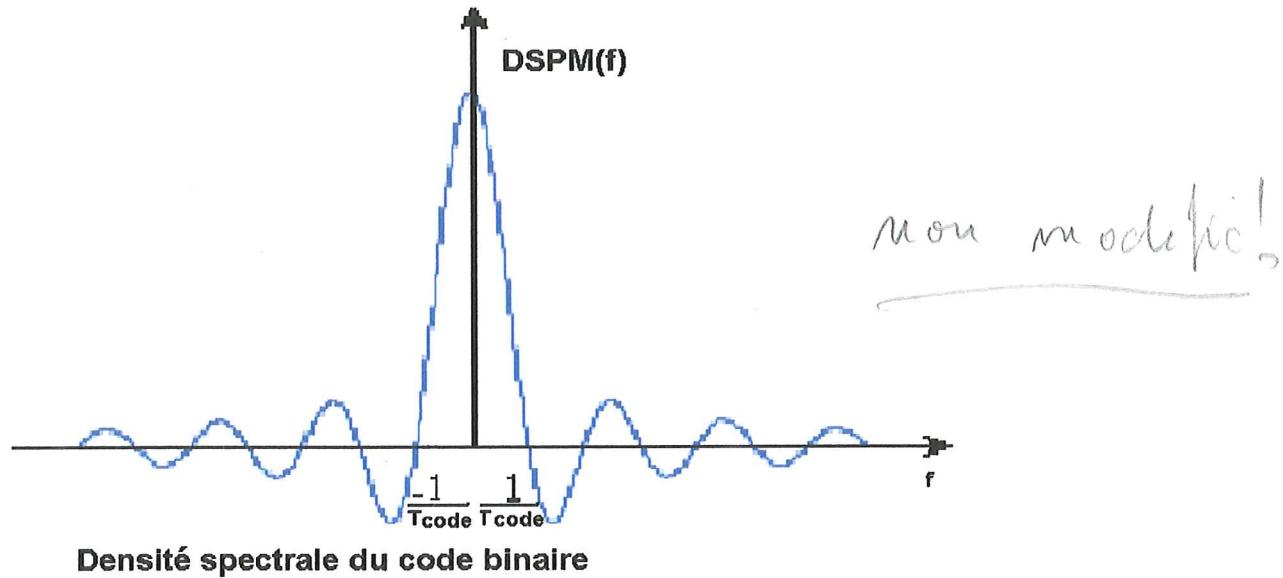

Les séquences sont choisies pour leurs propriétés mathématiques. Le bit de donnée est porté par une suite binaire de longueur maximale à  $N$  bits (SBLM- $N$ ). Ainsi, on définit un débit « code » ( $D_{code}$ )  $N$  fois plus rapide que le débit « data » ( $D_{data}$ ). La densité spectrale (DSP) de  $C_k(t)$  est limitée aux fréquences  $-1/T_{code}$  et  $1/T_{code}$  (filtre passe bas à  $1/T_{code}$ ).

On notera qu'une séquence binaire ( $D_{code} = 1/T_{code}$ ) à moyenne nulle  $x_{nrz}(t)$  bivalente (hauteur + ou -  $A$ ) porte la puissance moyenne constante  $A^2$  (en  $V^2$ ).

## Principe de l'accès multiple avec code :

Il existe plusieurs variantes : on décrit ci-dessous l'étalement par séquence directe (Direct Sequence Spread Spectrum).

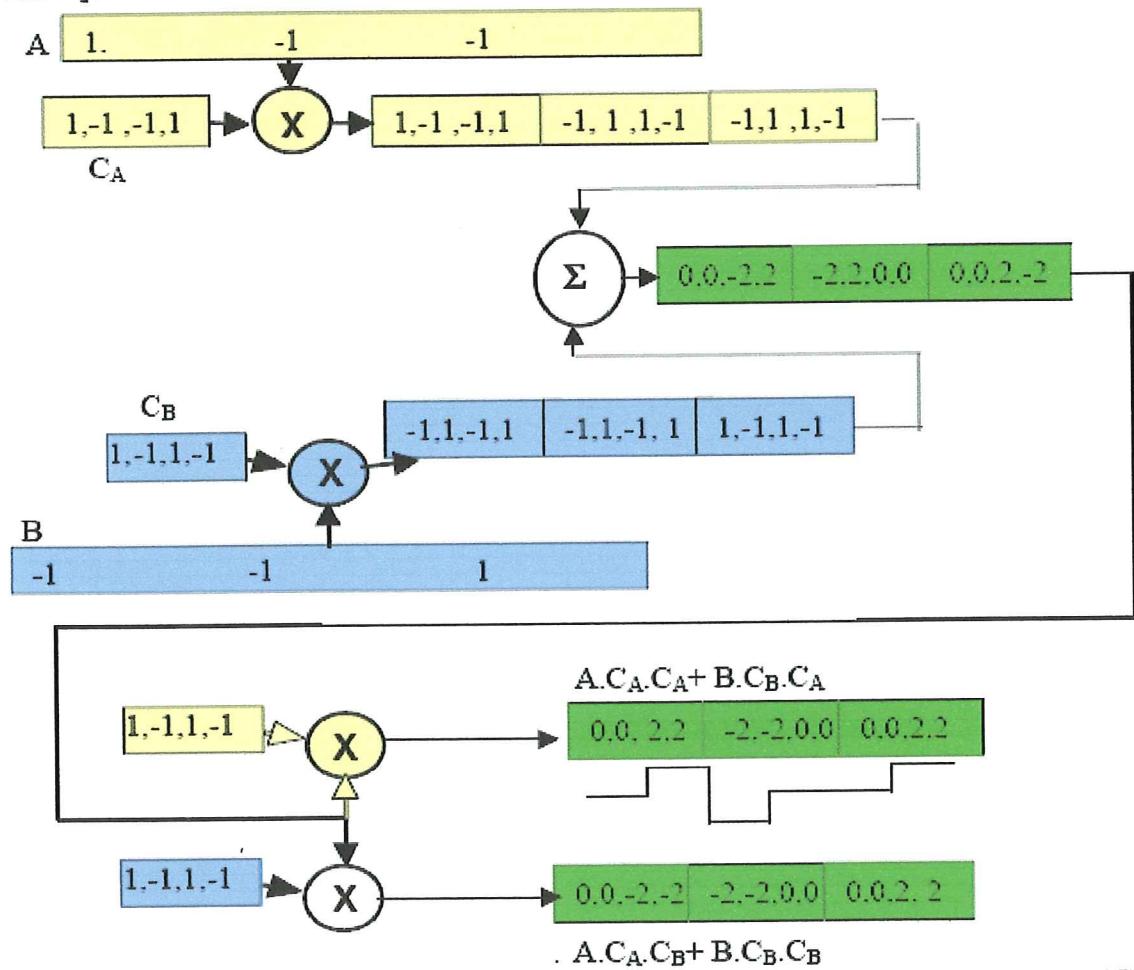

- Le message A de l'émetteur A, représentée par une séquence de +1, -1 traduisant la séquence de bits 1 et 0 logiques, est multiplié par un code : une séquence de +1 et -1 (les « chips ») judicieusement choisie, et dont les transitions sont  $m$  fois plus fréquentes. Idem pour un émetteur du message B: message multiplié par un code B.

- Les séquences produits  $A^*CA$  et  $B^*CB$  sont ajoutées et transmises.

- A la réception, le destinataire du message A multiplie la séquence reçue par le code CA, idem pour le destinataire du message B.

Si les codes sont bien choisis, sur la durée d'un bit, (donc de  $m$  chips), la moyenne de  $CA.CA$  et de  $CB.CB$  est égale à  $m/2$ , tandis que  $CA.CB$  a une moyenne nulle : Les codes CA et CB sont dits « orthogonaux » (Somme des produits des éléments correspondants [=produit scalaire]=0).

Exemple :

Remarque :

- En réception les signaux sur chaque durée d'un bit de message ont une moyenne non nulle, ce qui permet la reconstitution du signal par simple filtre passe bas. On préfère en fait mesurer la corrélation : la somme des produits code \* signal reçu sur la durée d'un bit.

- Les codes sont choisis tels que leur produit scalaire CA.CB soit nul et CA.CA soit maximum (codes orthogonaux = produit scalaire nul). On rappelle qu'un produit scalaire est la somme des produits des composantes correspondantes :  $u_1v_1 + u_2v_2$  pour deux vecteurs U et V de composantes  $u_1, u_2$  et  $v_1, v_2$ . Cette notion de produit scalaire n'est pas limitée aux vecteurs dans le plan, mais est générale. Le code est ici un vecteur dont les composantes sont les chips.

- Si l'on effectue une moyenne non pas sur les chips d'une période mais à cheval, les moyennes seront globalement plus faibles => ceci permet de synchroniser la réception pour certains systèmes, en recherchant la position où l'on obtient (en valeur absolue) un maximum. Les codes sont dans ce cas choisis tels que le produit scalaire d'un code par lui-même décalé soit pratiquement nul

### Génération de codes :

Un générateur est typiquement constitué de N bascules dont certaine (détermination mathématique) sont rebouclées à travers un ou exclusif (notation 1,0) ou une multiplication (notation +1,-1). Avec N étages, la longueur maximale des séquences pseudo-aléatoires est de  $2N - 1$  (les m-séquences). L'état tout à zéro est interdit (puisque auto entretenu). IS 95 utilise N=15. Le générateur en phase est construit sur le polynôme caractéristique (approche mathématique) :  $x^{15} + x^{13} + x^9 + x^8 + x^7 + x^5 + 1$  qui indique des bouclages sur les étages 0, 5, 7, 8, 9 13 et 15.

Exemple plus simple à trois étages : états : 001, 011, 111, 110, 101, 010, 100, puis à nouveau 001 (les bits entrant à droite [= ou exclusif des positions 1 et 3,] constituent la séquence). Ces séquences ont une fonction d'auto-corrélation avec un maximum pour zéro à  $2N - 1$ , et une valeur négligeable (-1) pour toute autre valeur du décalage.

Cette propriété permet de prendre comme ensemble de codes la même séquence avec les  $2N-1$  décalages possibles. Ces codes quasi-orthogonaux sont dits linéaires et n'offrent pas une protection (cryptage) très élevée : on peut les déchiffrer à partir d'une connaissance partielle de la séquence.

- **Code de Barker** : Les codes de Barker présentent une fonction d'auto corrélation de même allure que les m-séquences.

- **Gold codes** : Codes à inter corrélation et auto corrélation bornées, obtenus en additionnant (modulo 2) deux m-séquences appariées. Tous les codes ne sont pas équilibrés.

| L | $2^L - 1$ | paires de m-séquences | intercorrélations: 3 valeurs |    |    |      |

|---|-----------|-----------------------|------------------------------|----|----|------|

| 5 | 31        | [5,3][5,4,3,2]        | 7                            | -1 | -9 | -29% |

| 6 | 63        | [6,1][6,5,2,1]        | 15                           | -1 | 17 | -27% |

| 7 | 127       | [7,3][7,3,2,1]        | 15                           | -1 | 17 | -13% |

- Générateur de Walsh:

2N vecteurs de chacun 2N bits constituent un ensemble de codes parfaitement orthogonaux. Ils ont été obtenus comme colonnes des matrices de Walsh construites par récurrence :

$H_N = H_{N-1} H_{N-1}^* =$  matrice de Walsh à 2N lignes et colonnes.

$H_{N-1} H_{N-1}^{*}$

IS-95 utilise des mots de Walsh à 64 chips pour identifier les canaux sur la liaison directe.

### Propriété spectrale des codes

En réception, il suffit de connaître la séquence pour retrouver le code initial. Pour cela on utilise la corrélation entre la réception du message et la séquence connue.

On peut noter que l'étalement du spectre amène à diviser la puissance spectrale. L'idée est de transformer le signal en bande relativement étroite en un signal qui a l'apparence d'un bruit sur une bande large lors de la transmission.

Définition du canal transmis par étalement de spectre :

Il faut le code à moyenne nulle ( $\langle NRZ \rangle = 0$ ) et le module de la porteuse  $b * \cos^*(wpt)$  dans un multiplicateur de facteur  $\beta$ .

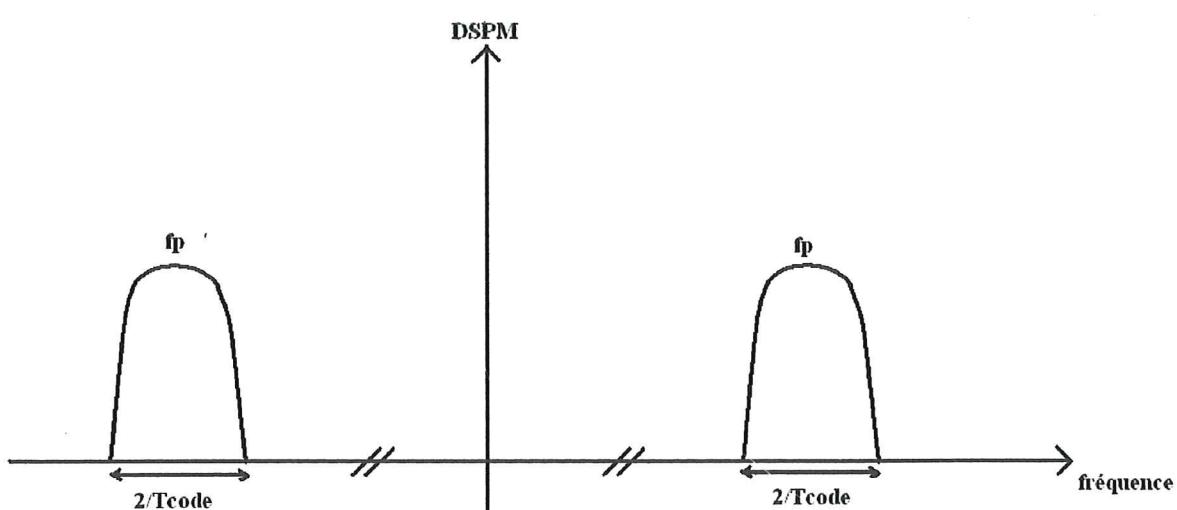

Le canal centré autour de  $f_p$  de longueur  $2/T_s$  est décrit par :

$$y_{CDMA}(t) = x_{NRZ}(t) \cdot b * \beta * \cos^*(2\pi f_p t) = x_{NRZ}(t) / A.$$

Le théorème du changement de fréquence dans la DSPM(f) permet de dire que :

$$DSPM(f)_{CDMA} = b^2/4 (\text{sincar } \pi (f-f_p) T_{code})^2 + b^2/4 (\text{sincar } \pi (f+f_p) T_{code})^2$$

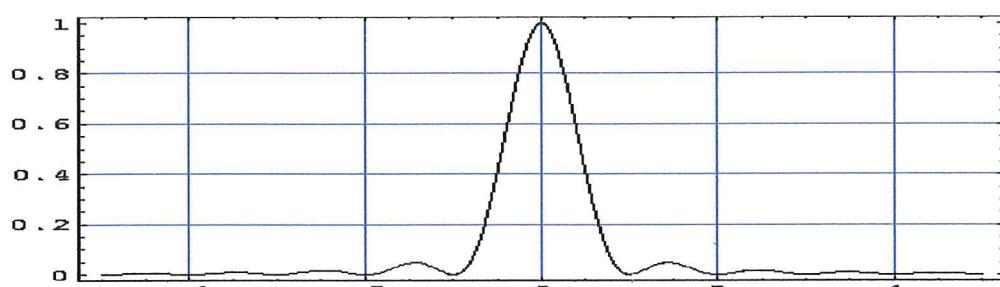

Allure d'un sinus cardinal au carré

DSPM(f) CDMA représenté par des lobes à la place des sinus cardinaux

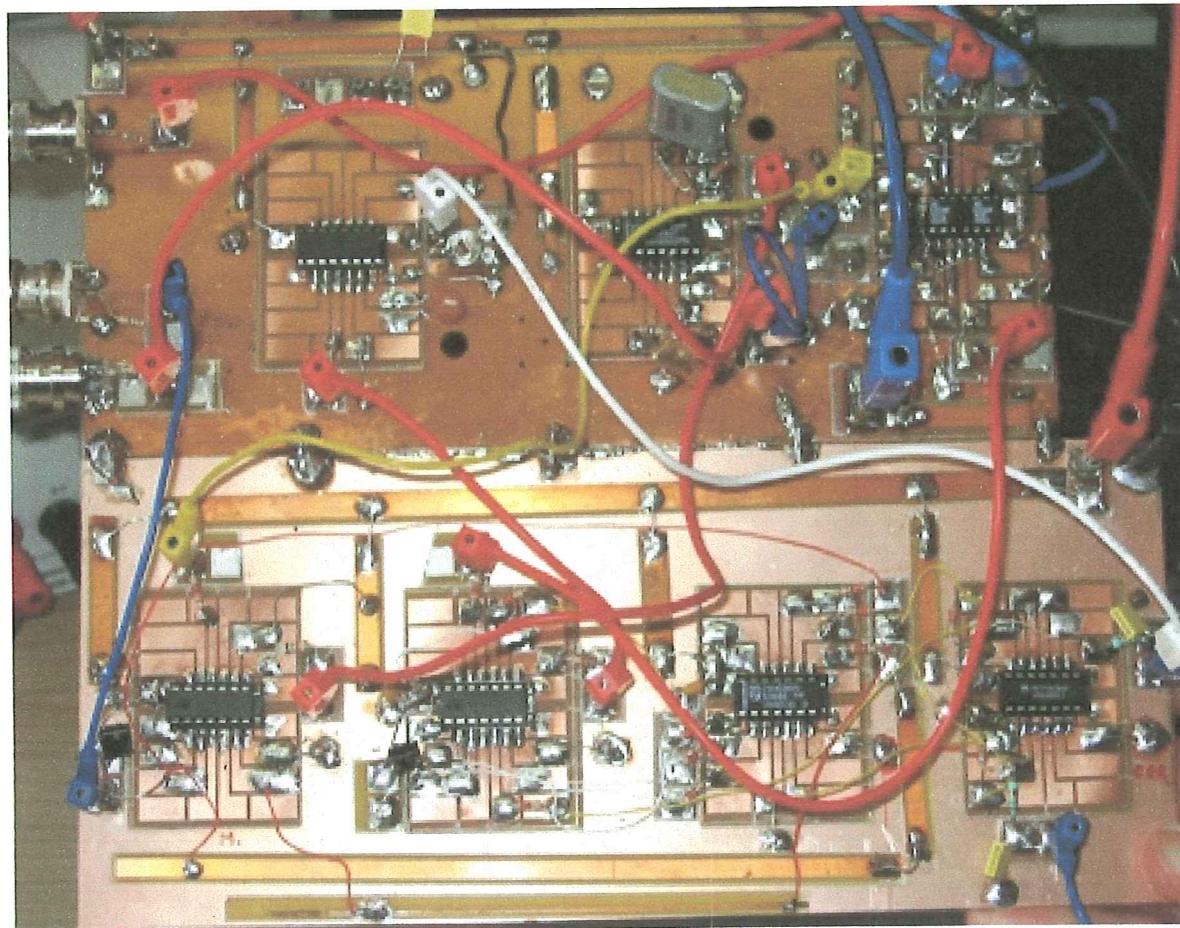

## 2) - Essais et matérialisation des fonctions

Dans la partie précédente, nous avons expliqué comment on utilisait la transmission par CDMA. On a vu qu'elle se faisait à l'aide d'une génération de séquences binaires. Ces séquences permettent de coder des données d'informations. Pour cela, on doit multiplier la séquence avec les informations. Lors de la transmission, ce signal sera étendu au niveau fréquentiel ce qui le rendra pratiquement indétectable. Pour récupérer les données, il faudra remultiplier le signal avec la même séquence non déphasé.

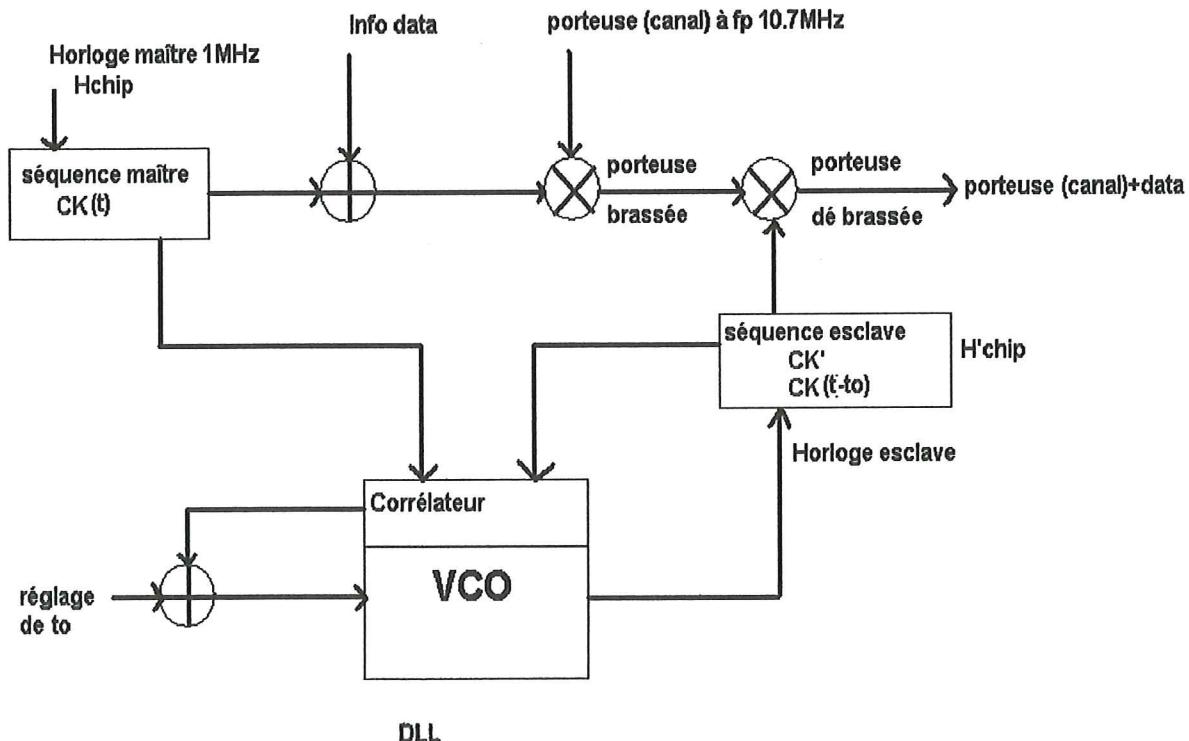

Synoptique de notre carte didactique

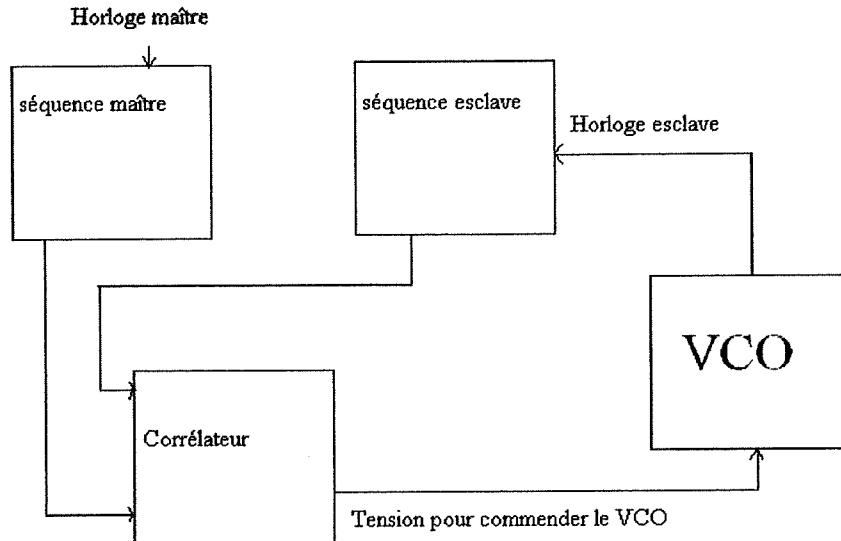

Cette séquence doit être périodique, c'est pour cela que l'on utilise un générateur à suite binaire de longueur maximale (SBLM). Pour la réception des données, la séquence binaire permettant le décodage devra être la même que la séquence envoyée, c'est-à-dire en fréquence et en phase. De ce fait, l'utilisation d'un système mettant en évidence la corrélation de deux séquences et d'un VCO est nécessaire.

Nous utiliserons aussi deux multiplieurs ainsi que plusieurs composants pour générer l'horloge « maître ». Une porteuse permettra au transport.

## 2.1) Séquenceurs fournissant les SBLM

### 2.1.1) Explication d'une SBLM et schéma de principe

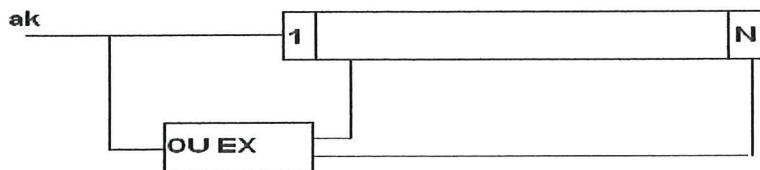

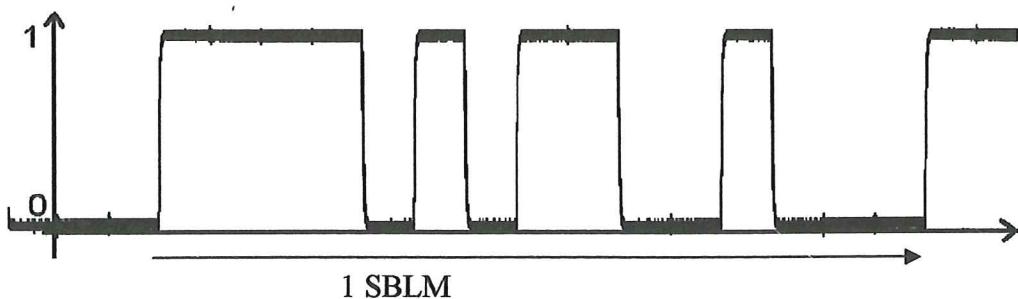

Une SBLM est une suite binaire qui se répète. Elles nous servent dans notre cas à la génération de code pour notre CDMA. Elle possède une longueur maximale qui correspond au nombre de  $N$  bascules et du au bouclage de ces bascules sur l'entrée. Selon les deux sorties prises en compte pour faire ce bouclage, il s'agit ou pas de SBLM. Lorsque la séquence est très longue mais qu'elle se répète, on peut parler de séquence pseudo aléatoire. Le nombre d'étage  $N$  définit la longueur maximal de la séquence qui est égal à  $2N-1$ . Le bouclage est fait par un ou exclusif de deux entrées (séquences pris en retard après  $N$  bascules) sur l'entrée non retardée.

Suite Binaire Obtenue

| Ak | Ak-1 | Ak-2 | Ak-3 |

|----|------|------|------|

| 0  | 1    | 1    | 1    |

| 0  | 0    | 1    | 1    |

| 1  | 0    | 0    | 1    |

| 0  | 1    | 0    | 0    |

| 1  | 0    | 1    | 0    |

| 1  | 1    | 0    | 1    |

| 1  | 1    | 1    | 0    |

| 0  | 1    | 1    | 1    |

Exemple si  $ak=1$  au début, le bit va se déplacer dans le séquenceur. Pendant ce temps, les 2 bouclages sont encore à l'état 0,  $ak$  reste donc à 1. A un moment un bouclage va finir par prendre l'état logique 0 et l'autre 1 à cause des bascules mémoires  $N$ . D'après la table du ou exclusif  $ak$  va prendre comme état 0. Ce processus se poursuit indéfiniment dans certain cas de bouclage.

Voici une SBLM que l'on a observé avec comme bouclage  $ak-1$   $ak-4$ .

Résultat trouvé selon les bouclages :

| N | Suite ak             | SBLM ? | P0    | P1    |

|---|----------------------|--------|-------|-------|

| 3 | <b>ak=ak-1⊕ ak-3</b> | oui    | 3/7   | 4/7   |

|   | <b>ak=ak-2⊕ ak-3</b> | oui    |       |       |

| 4 | <b>ak=ak-1⊕ ak-4</b> | oui    | 7/15  | 8/15  |

|   | <b>ak=ak-2⊕ ak-4</b> | non    |       |       |

|   | <b>ak=ak-3⊕ ak-4</b> | oui    | 7/15  | 7/15  |

| 5 | <b>ak=ak-1⊕ ak-5</b> | non    |       |       |

|   | <b>ak=ak-2⊕ ak-5</b> | oui    | 15/31 | 16/31 |

|   | <b>ak=ak-3⊕ ak-5</b> | oui    | 15/31 | 16/31 |

|   | <b>ak=ak-4⊕ ak-5</b> | non    |       |       |

| 7 | <b>ak=ak-1⊕ ak-7</b> | oui    |       |       |

|   | <b>ak=ak-2⊕ ak-7</b> | non    |       |       |

|   | <b>ak=ak-3⊕ ak-7</b> | oui    |       |       |

|   | <b>ak=ak-4⊕ ak-7</b> | oui    |       |       |

|   | <b>ak=ak-5⊕ ak-7</b> | non    |       |       |

|   | <b>ak=ak-6⊕ ak-7</b> | oui    |       |       |

P0 et P1 correspondent à la proportionnalité d'avoir l'état logique 1 et 0 dans une séquence. Les remarques que on a tiré sont la longueur des SBLM est égal à  $2^N - 1$ . La proportionnalité d'avoir un 0 est de  $[2^{N-1} - 1] / [2^N]$  et la proportionnalité d'avoir un 1 est de  $[2^{N-1}] / [2^N]$ .

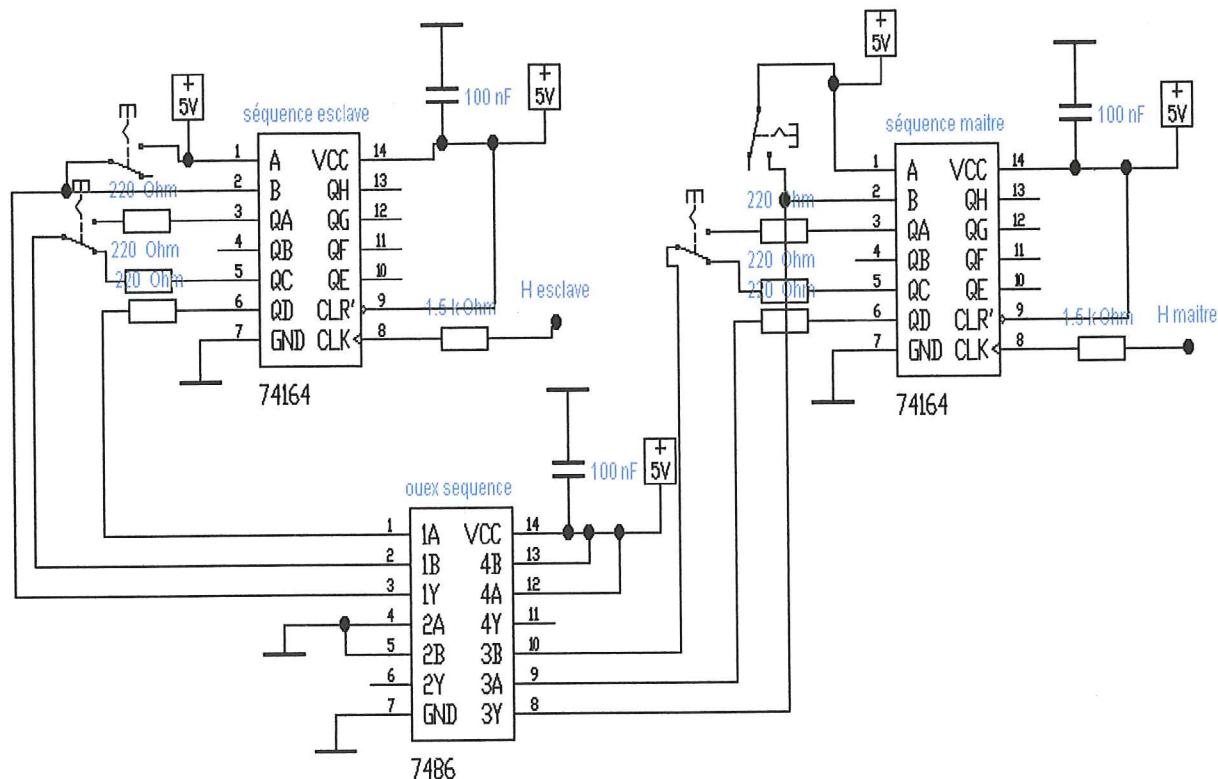

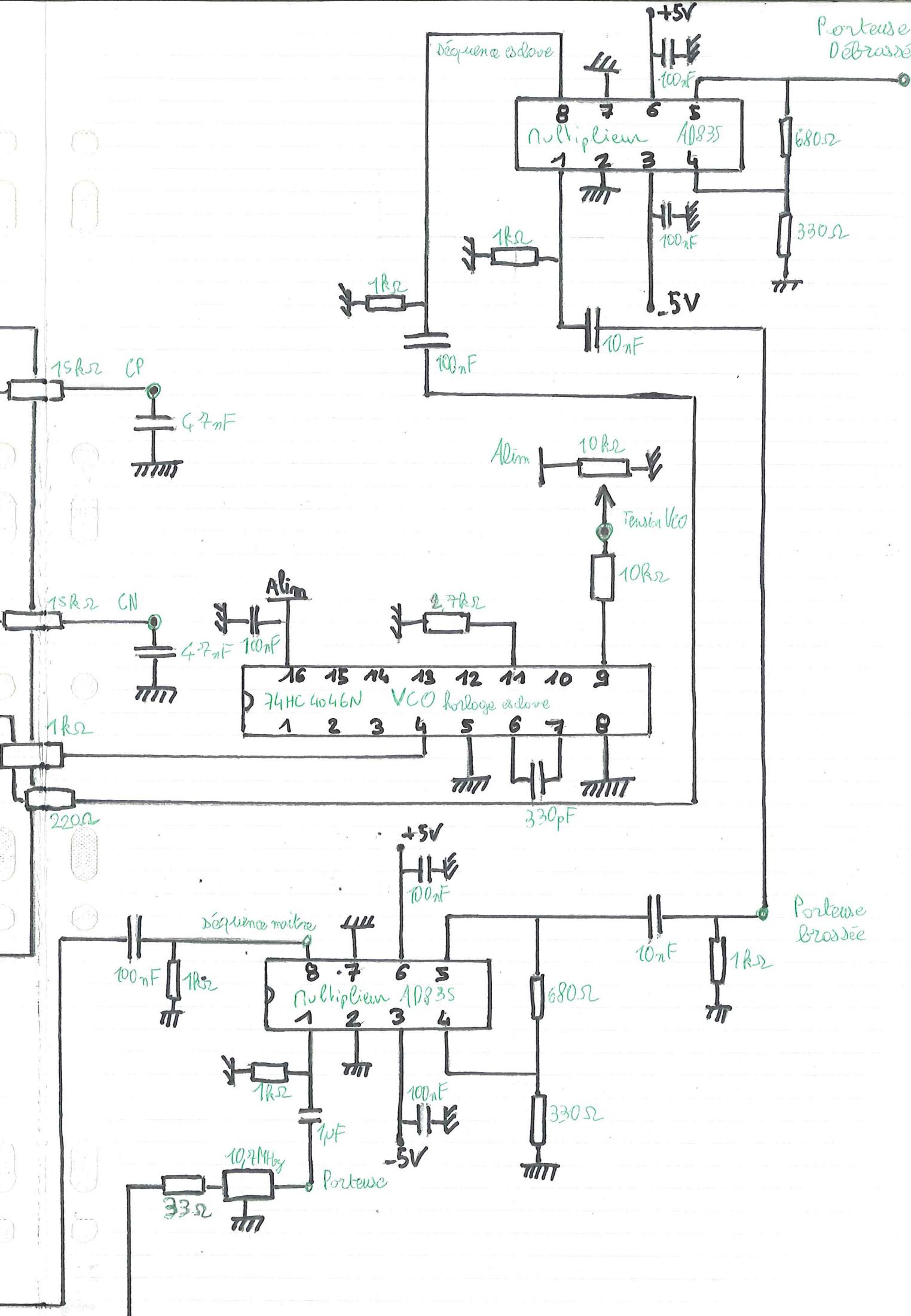

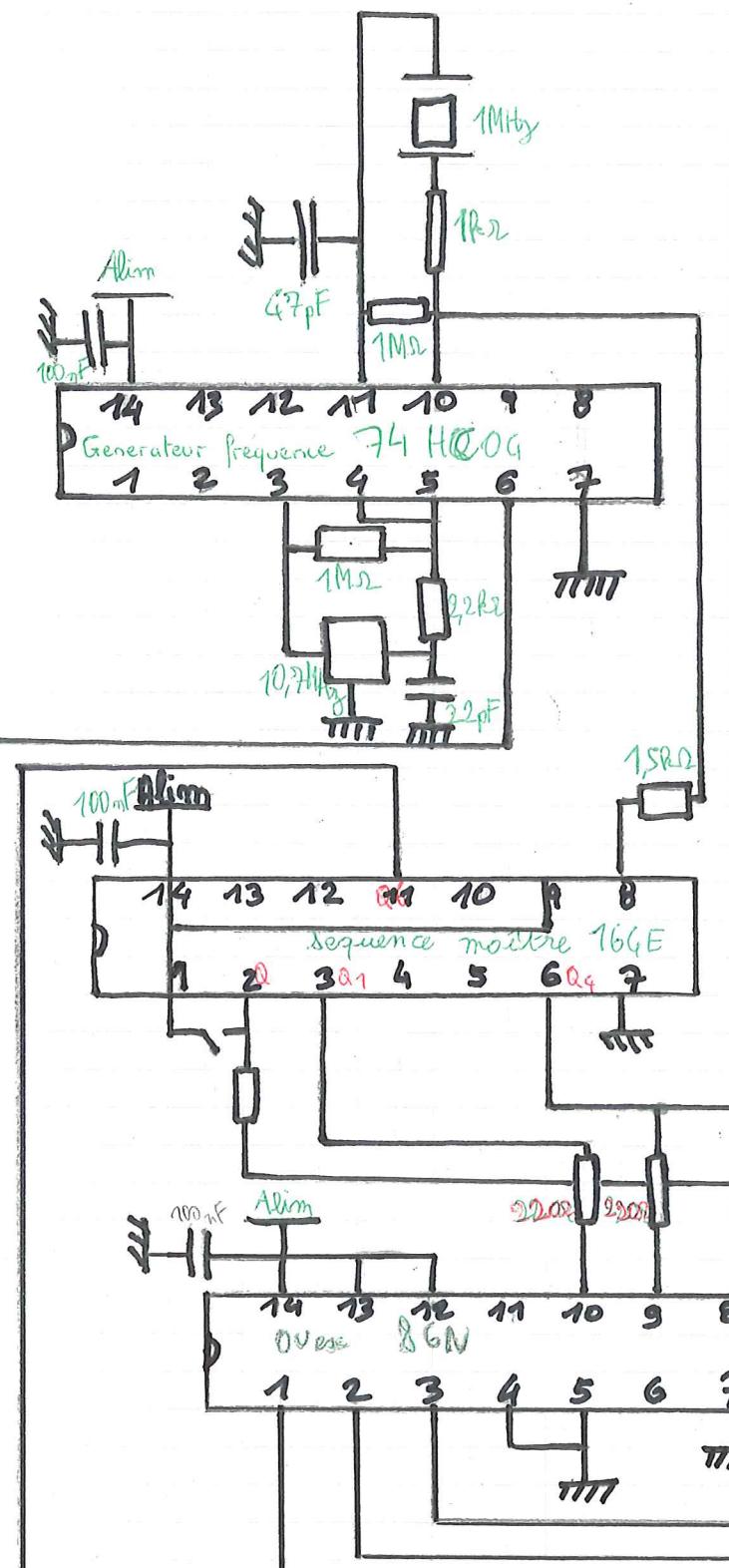

### 2.1.2) Rôle et schéma électrique

Le rôle d'une SBLM pour un CDMA est de coder les bits de données. Un 1 logique de donnée sera représenté par la SBLM et 0 par son complément comme expliqué précédemment lors du principe du CDMA. Il faut donc créer une SBLM à l'émission et aussi à la réception pour pouvoir récupérer les données. De cette manière les données envoyées ne peuvent pas être lues sans la connaissance de cette séquence et de plus au niveau de la fréquence, le signal des données n'existe plus, son énergie est étalée, ce qui rend encore plus difficile sa lecture si on ne la connaît pas.

Pour concevoir une SBLM, nous avons besoin de bascules N (HCT74164 voir annexe) et de ou exclusif (7486 voir annexe). Dans notre cas on utilisera une séquence pas trop longue (N=4) pour la compréhension des phénomènes.

- séquenceur (bascule N) maître et esclave

- Patte 14: 5V couplé avec un condensateur de 100nF

- Patte 7 : Masse

- Patte 1 et 9 : 5V et Switch avec patte 2 pour démarrer la séquence

- Patte 2 : entrée ak; sortie du ou ex

- Patte 3 : sortie ak-1; entrée du ou ex avec impédance de 220Ω

- Patte 6 : sortie ak-4; entrée du ou ex avec impédance de 220Ω

- Patte 8 : entrée horloges 1 MHz avec impédances de 1,5kΩ

- ou exclusif :

- Patte 14: 5V couplé avec un condensateur de 100nF

- Patte 7 : Masse

- Pattes 1 et 2; 4 et 5; 9 et 10; 12 et 13 entrées ou exclusif on utilisera les pattes 1 et 2 ainsi que 9 et 10 et les pattes 4, 5, 12, 13 on les forcera à un état logique

- Pattes 3, 6, 8, 11 sortie ou exclusif, on utilisera les pattes 3 et 8

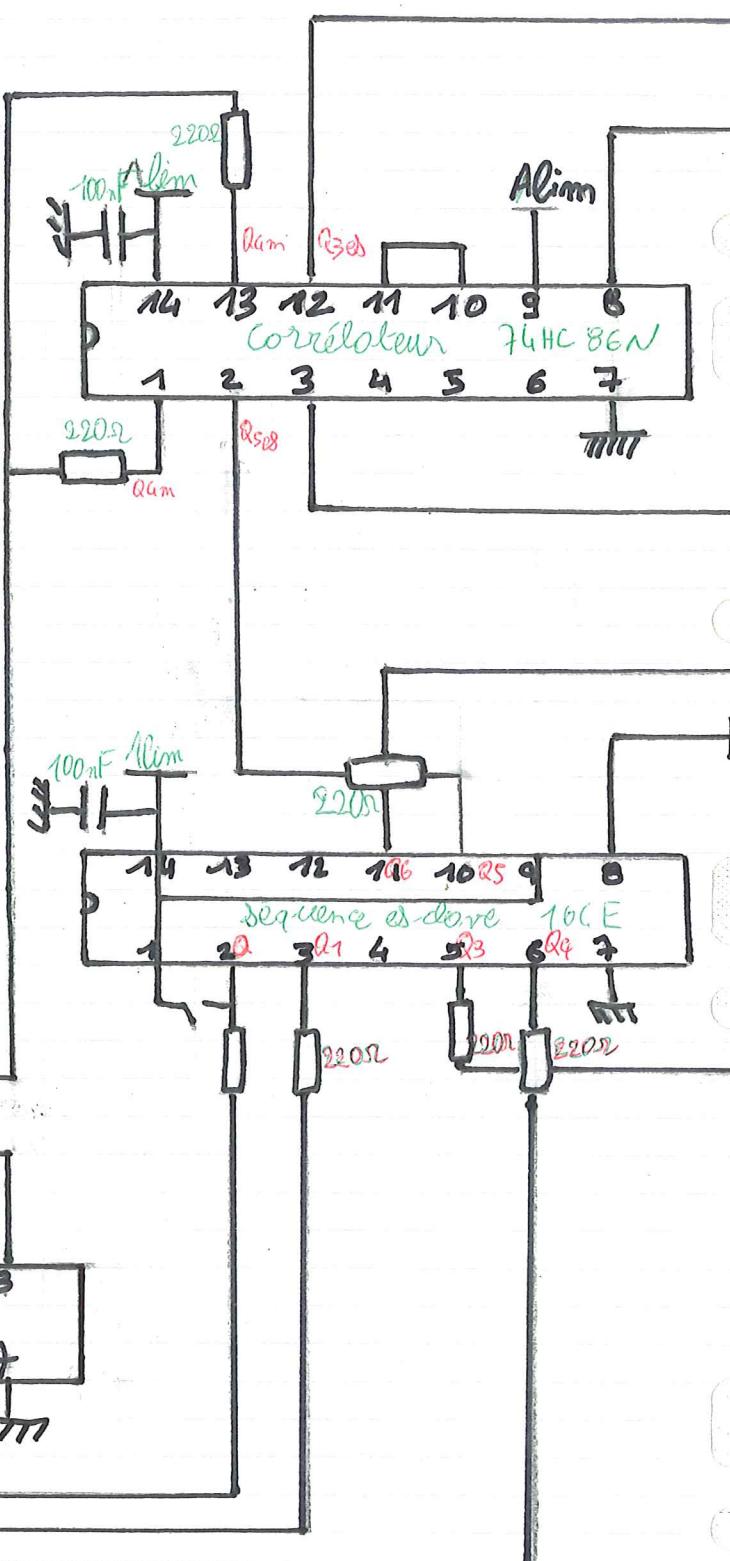

## 2.2) Corrélateur

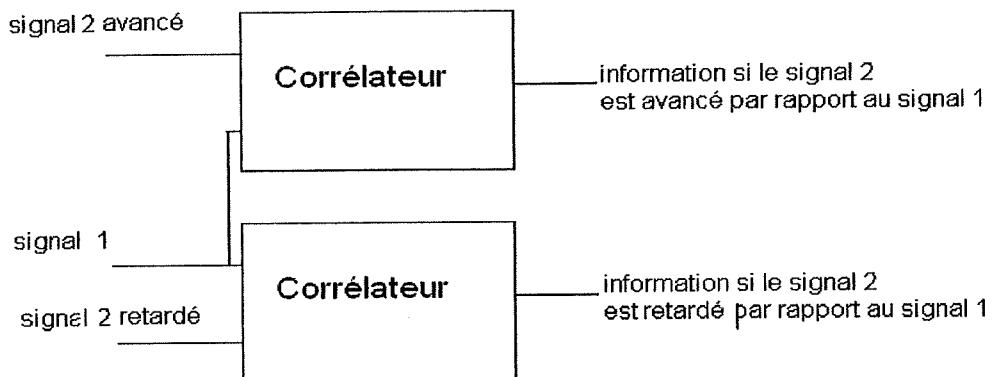

### 2.2.1) Explication et schéma de principe

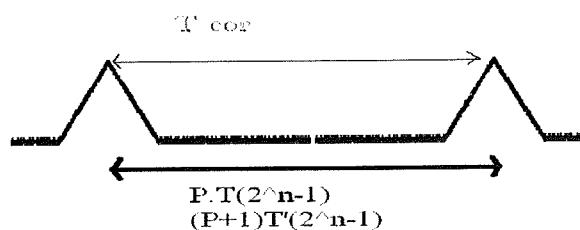

Un corrélateur permet de mettre en relation deux signaux qui sont identiques mais décalés dans le temps. Il permet de donner une tension qui indique si l'un des deux signaux est en retard ou en avance. Dans un premier temps, on a étudié la corrélation de deux quartzs à 4,9152MHz que l'on utilise comme horloge.

Dans un premier temps, on a étudié la corrélation avec  $n=4$  de deux quartzs à 4,9152MHz que l'on utilise comme horloge.

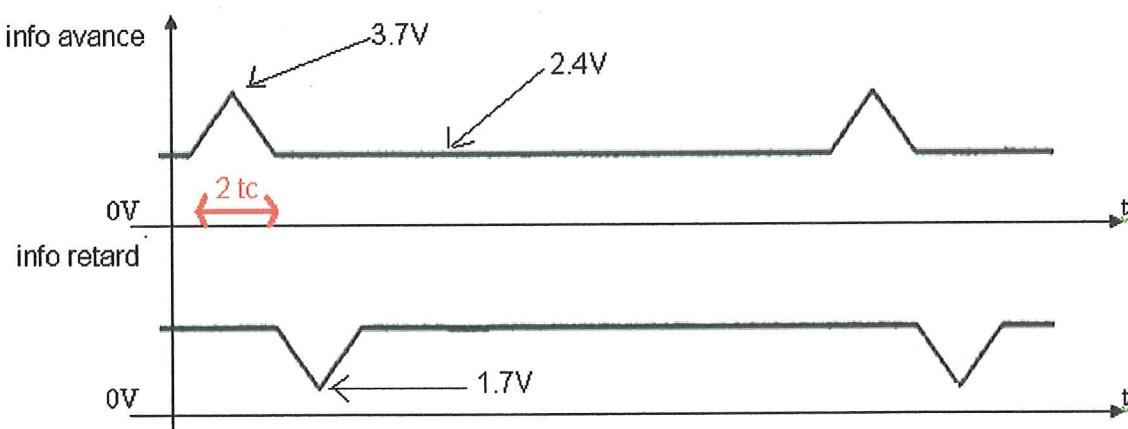

Information retardée :

$P$  : période séquence

Calcul de  $T_{cor}$  :

$$T_{cor}=P.T(2^n-1)$$

$$T_{cor}=(P+1).T'(2^n-1)$$

$$P.T(2^n-1)=(P+1).T'.(2^n-1)$$

$$P.T=(P+1).T'$$

$$P.T=P.T'+T'$$

$$P.T-P.T'=T'$$

$$P=T'/(\Delta T) \quad T-T'=\Delta T$$

$$T_{cor}=(T'.T(2^{n-1}))/\Delta T$$

$$1/\Delta T=1/(T-T')=1/((1/F)-(1/F'))=FF'/\Delta F$$

$$T_{cor}=(T'.T.F.F'(2^{n-1}))/\Delta F$$

$$T_{cor}=(2^n-1)/\Delta T$$

Vérification  $n=4$

$$T_{cor}=3.5s$$

$$2^{n-1}=15$$

$$3.5/15=1/\Delta F$$

$$\Delta F=4.3Hz$$

Fréquence quartz = 4.91252 MHz d'où  $\Delta F$  = Fréquence quartz/10<sup>6</sup>=4.9 Hz. Ce qui correspond à ce que l'on obtient. Tolérance des quartzs <= 10<sup>-6</sup> soit ils dévient de 4.3 Hz.

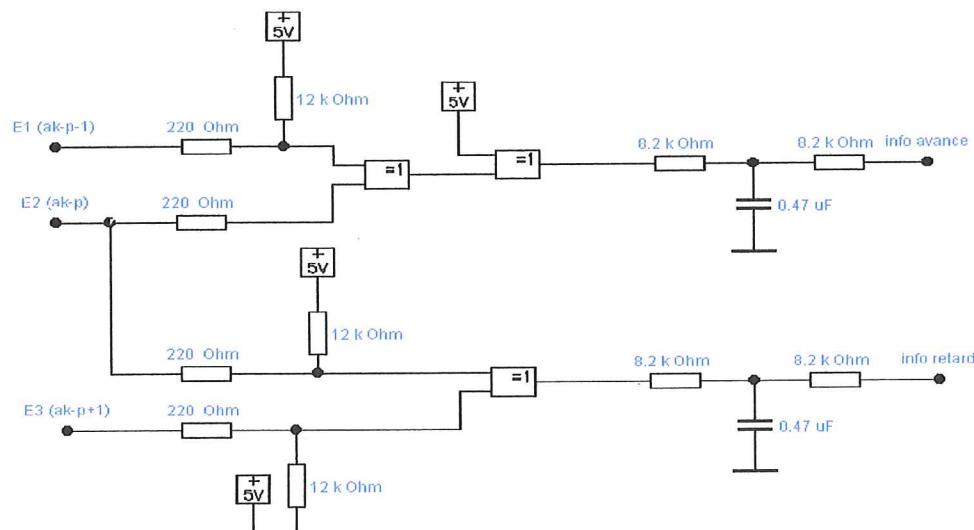

### 2.2.2) Rôle et schéma électrique

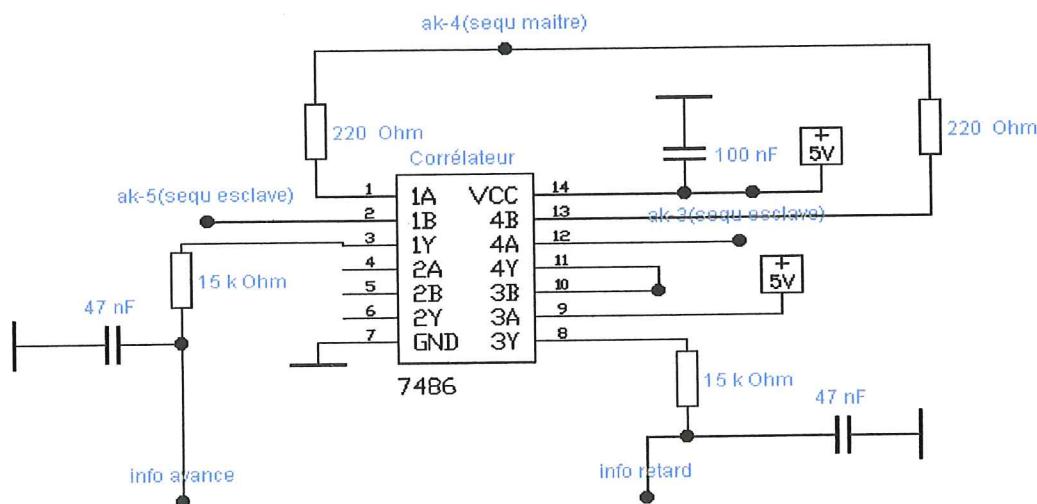

Le corrélateur va nous permettre d'avoir une information sur la différence de fréquence et le déphasage entre la séquence maître (émission sert à coder les data) et la séquence esclave (réception sert à récupérer la porteuse ou data). Le corrélateur est un simple ou exclusif.

Comme signal 1, on prendra la séquence « maître » sur la bascule 4.

Comme signal 2 retardé, on prendra la séquence « maître » sur la bascule 5.

Comme signal 1, on prendra la séquence « maître » sur la bascule 3.

On souhaite inverser l'information de retard pour que l'on puisse la différencier avec l'information d'avance.

Résultat trouvé :

tc correspond à un temps chip soit pour une séquence avec  $N=4$ , il y a  $15 \text{ tc} = 2^4 - 1$

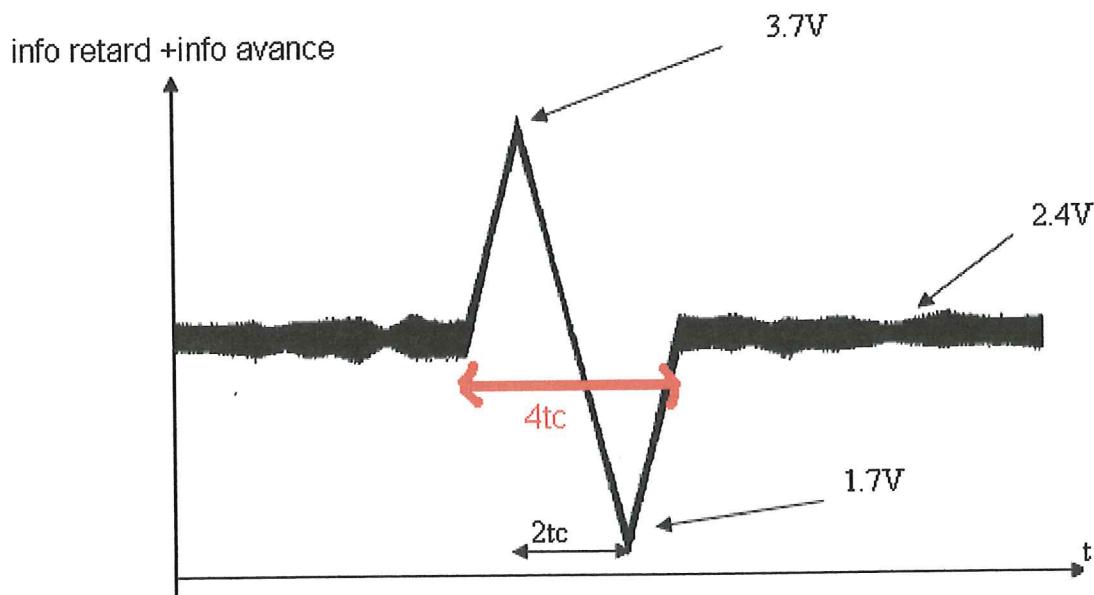

Maintenant ce que nous souhaitons c'est ajouter ces 2 informations, pour avoir une information proportionnelle à l'avance et au retard entre les deux séquences. Cette information nous permettra de modifier le déphasage de la séquence esclave pour quelle s'approche le plus possible de la séquence maître.

Pour cela, il suffit d'ajouter les 2 courants.

- ou exclusif (voir annexe HCT86N) :

- Patte 14: 5V couplé avec un condensateur de 100nF

- Patte 7 : Masse

- Pattes 1 et 2; 4 et 5; 9 et 10; 12 et 13 entrées ou exclusif on utilisera les pattes 1 et 2 pour ainsi que 12 et 13 et les pattes 10 et 9 pour inverser l'info retard

- Pattes 3, 6, 8, 11 sortie ou exclusif, on utilisera les pattes 3,8 et 11 sur les pattes 8 et 11 que l'on doit relier pour ajouter les courants.

A la sortie des informations, on met en place un filtre passe bas pour éliminer les perturbations.

Obtention après l'ajout des courants :

## 2.3) Horloge « maître » et « esclave »

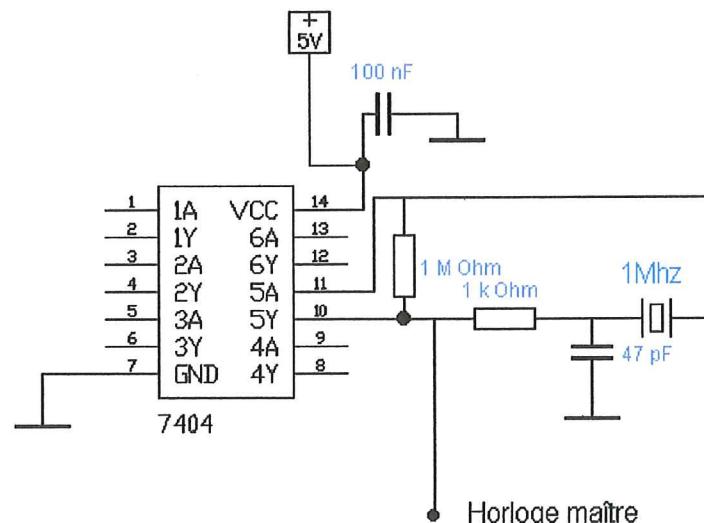

### 2.3.1) Horloge « maître »

- Rôle : le rôle de l'horloge « maître » est qu'il sert aux bascules N dans le séquenceur « maître ». Nous la fixons à 1 MHz, plusieurs montages ont été réalisés. Un avec un 74HC4060 qui ne nous permettait pas d'avoir une fréquence assez élevée. Ce montage permettait à l'aide d'un résonateur de 4 Mhz rentrant en résonance (obtention d'un sinus), et du 74HC4060 (plusieurs bascules D en série), d'avoir un signal carré. Donc à chaque branche de sorties, on avait la fréquence divisée par deux et sous forme d'une horloge 2, 4, 8, 16, 32, 64... Il suffisait donc d'utiliser la sortie qui divise la fréquence par quatre ( $4 \text{ Mhz}/4 = 1 \text{ Mhz}$ ), mais la division la moins élevée disponible est de seize. Il faut utiliser un résonateur de 16 Mhz pour avoir une horloge de 1 Mhz. On a du changer de montage car on ne possédait pas de résonateur à 16 Mhz.

On a donc utilisé donc un montage avec un 74HCT04 (inverseur).

- Schéma électrique

Ce montage a été pris dans la datasheet du composant.

### 2.3.2) Horloge esclave

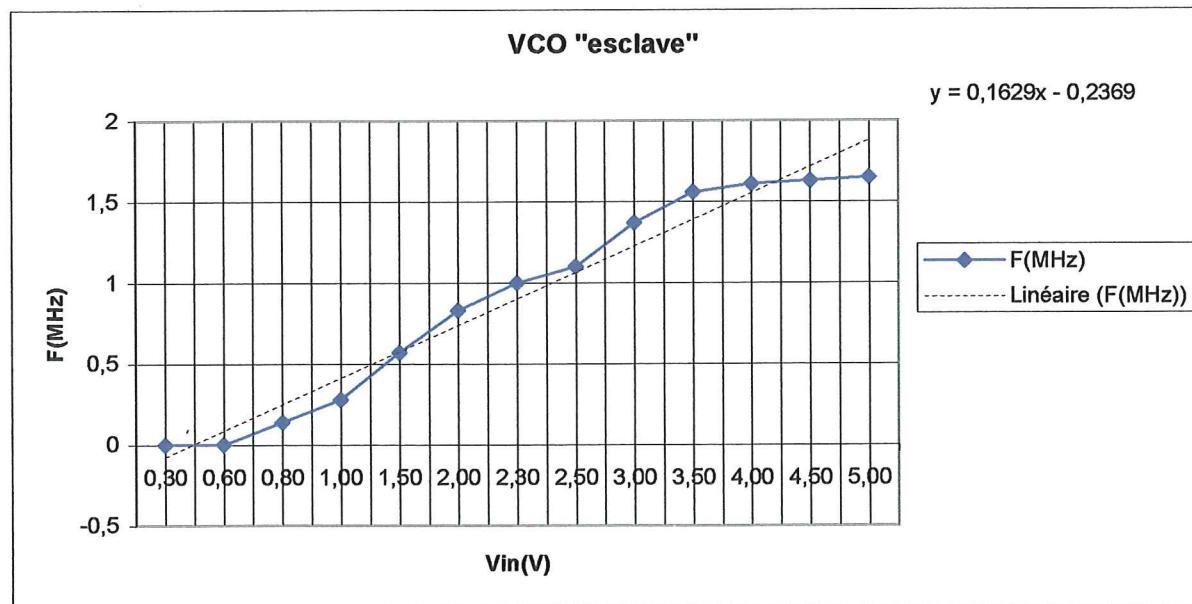

- Rôle : le rôle de l'horloge esclave est qu'elle sert aux bascules N dans le séquenceur esclave. Elle sera contrôlée par une tension venant du corrélateur pour que les fréquences d'horloges maître soit la même que l'esclave. Nous avons mis en place un potentiomètre qui nous permet de jouer sur la tension d'entrée, ce qui entraînera une variation de la fréquence d'horloge esclave donc au réglage fin entre l'avance et le retard des 2 séquences.

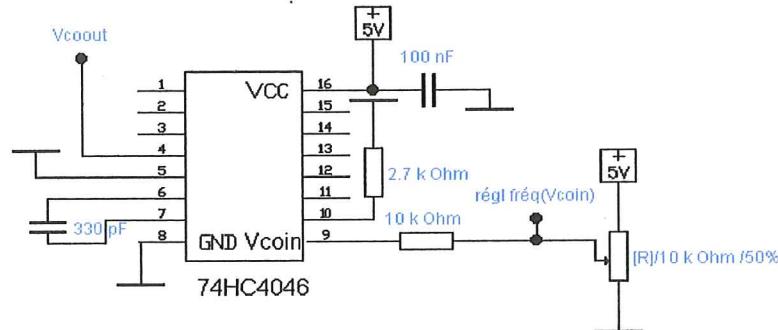

- Schéma électrique

régl fréq est la sortie du corrélateur

$V_{CO_{out}}$  est l'horloge esclave

Ce montage a été pris dans la datasheet du composant.

Relevé fréquence d'horloge en fonction de la tension VCO

## 2.4) Mise en place d'une porteuse (canal)

#### 2.4.1) Rôle

Le rôle de la porteuse est de transporter l'information data codée par une séquence code dans un canal de transmission autour de sa fréquence qui sera pour nous de 10,7 MHz. Cette porteuse est une sinusoïde qui a pour équation  $y(t) = a \cos(2\pi f_p t)$

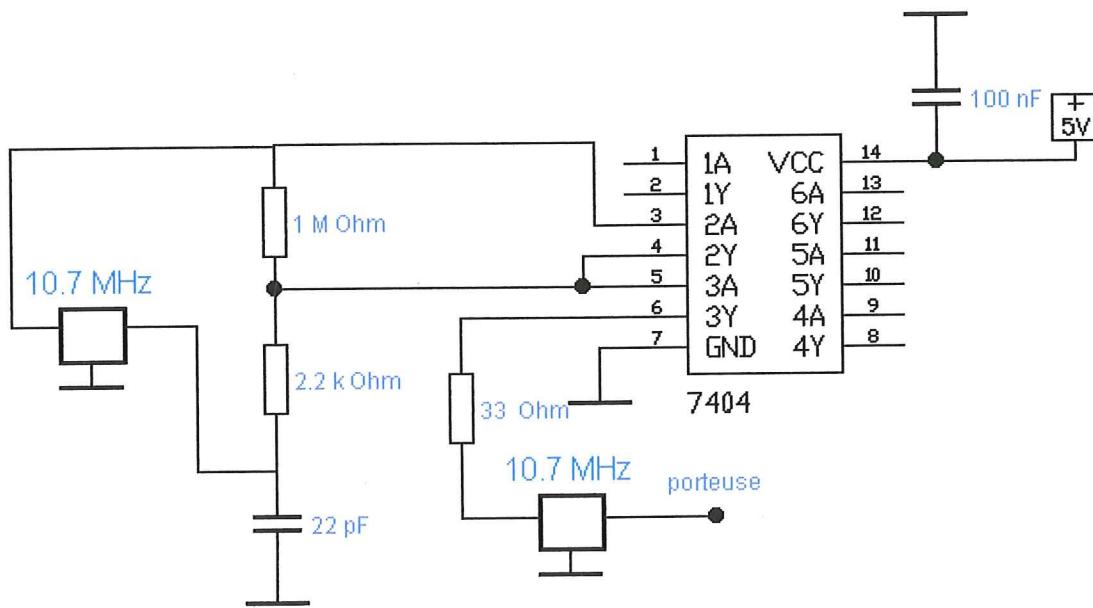

#### 2.4.2) Schéma électrique

Ce montage a été pris dans la datasheet du composant.

Le résonateur crée une sinusoïde qui entre dans un inverseur. Cette sinusoïde est mise en forme d'un carré dans un autre inverseur pour rendre le montage indépendant par rapport au reste de la carte. Il sera remis sous la forme d'une sinusoïde par un autre résonateur. Lors des relevées, on obtient une amplitude de 1V crête crête.

## 2.5) Mise en place du brassage et du dé brassage de la porteuse

### 2.5.1) Porteuse brassée

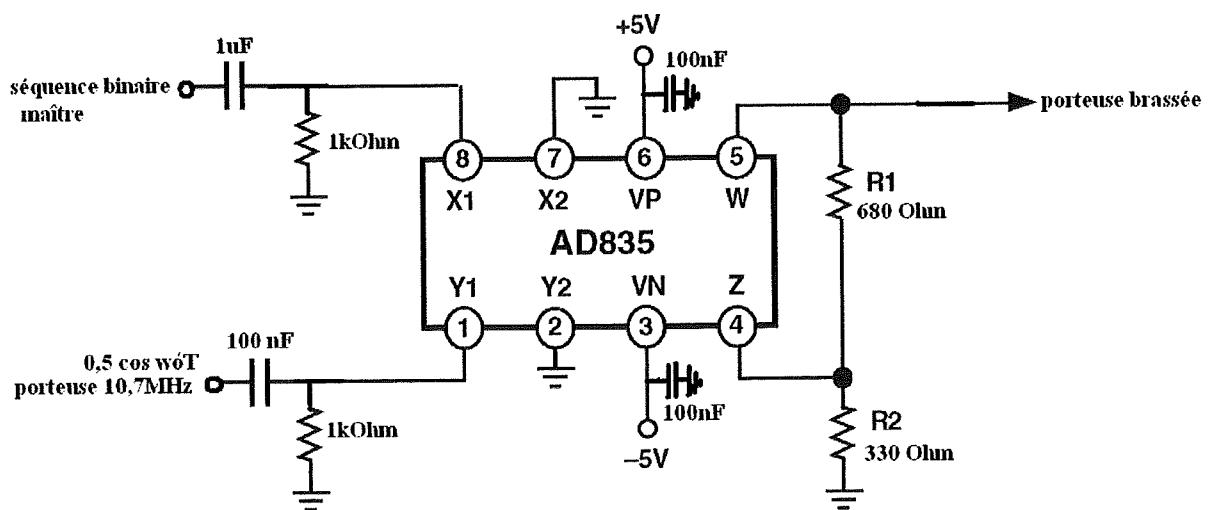

- Rôle : Lors d'une transmission par CDMA, le but est d'envoyer des données codées sur un support de canal. C'est pour cela que la porteuse a été réalisée précédemment pour ensuite être multipliée par la séquence code  $C_k(t)$ . Ainsi, on réalise une porteuse brassée qui va circuler dans le support de canal. De ce fait, on va pouvoir réaliser un étalement de spectre autour de la fréquence porteuse qui est de 10.7 MHz. L'étalement de spectre est une des principales caractéristiques de la transmission par CDMA.

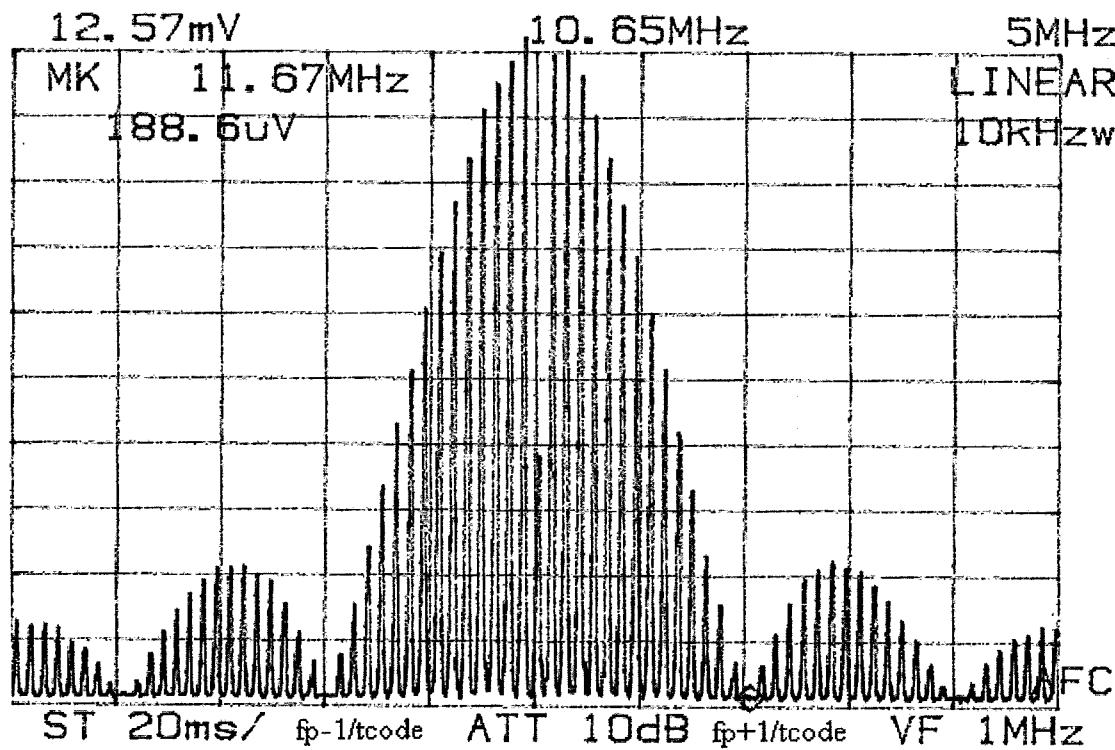

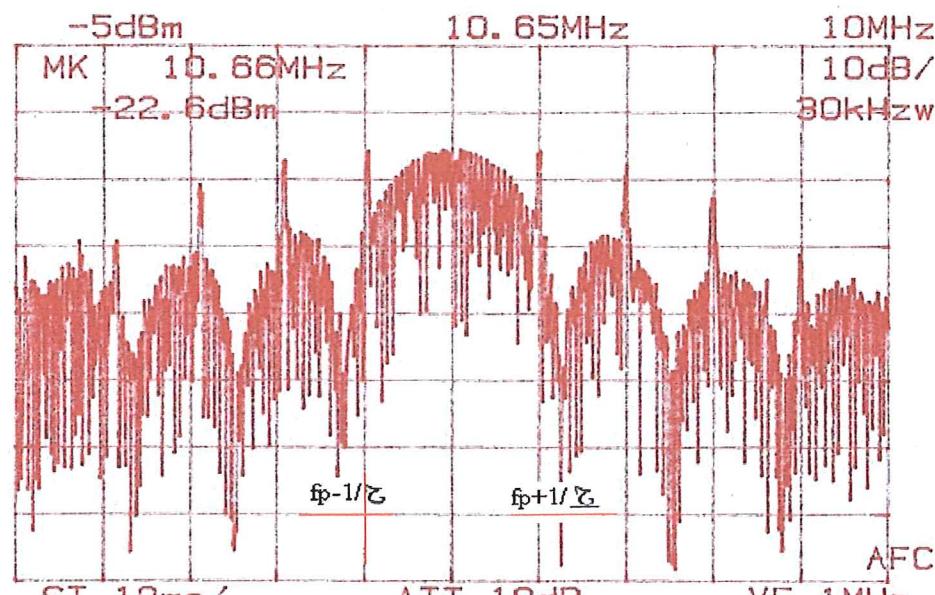

On observe ce résultat lorsque l'on fait la représentation fréquentielle (courbe).

On peut expliquer ce résultat théoriquement :

On obtient la DSPM de la séquence  $C_k$  en bande de base, en utilisant la transformée de Fourier de l'équation de l'auto-corrélation  $R(\tau)$ .

Où  $R(\tau) = 1/T_{code} * \int_{-\infty}^{\infty} (C_k(t) * C_k(t-\tau)) dt$

Ainsi  $R(f) = A^2 * T_{code} * (\text{sinc}(\pi * f * T_{code}))^2$  (en  $V^2/\text{Hz}$ )

On observe un sinus cardinal au carré entre  $f_p - 1/T_{code}$  et  $f_p + 1/T_{code}$ .

Formons la porteuse brassée par le code (chip)  $C_k$ .

Qui sera matérialisé par un changement de signe du à  $C_k$ .

Donc plutôt décrit par :  $a * \cos(wpt) * \text{signe}[C_k(t)]$ .

On a  $s(t) = a * \cos(wpt) * C_k(t)$

On utilise le théorème du changement de fréquence qui consiste à faire la translation en  $-f_p$  et  $f_p$  de la DSPM en bande de base.

D'où on obtient,

$s(f) = a^2/4 * T_{code} * [\text{sinc}(\pi * T_{code} * (F + f_p))]^2 + a^2/4 * T_{code} * [\text{sinc}(\pi * T_{code} * (F - f_p))]^2$

On observe ainsi deux sinus cardinaux au carré aux fréquences  $f_p$  et  $-f_p$ .

La puissance de la porteuse brassée est celle de la porteuse initiale donc  $a^2/2$  en  $V^2$ .

spectre de la porteuse brassée

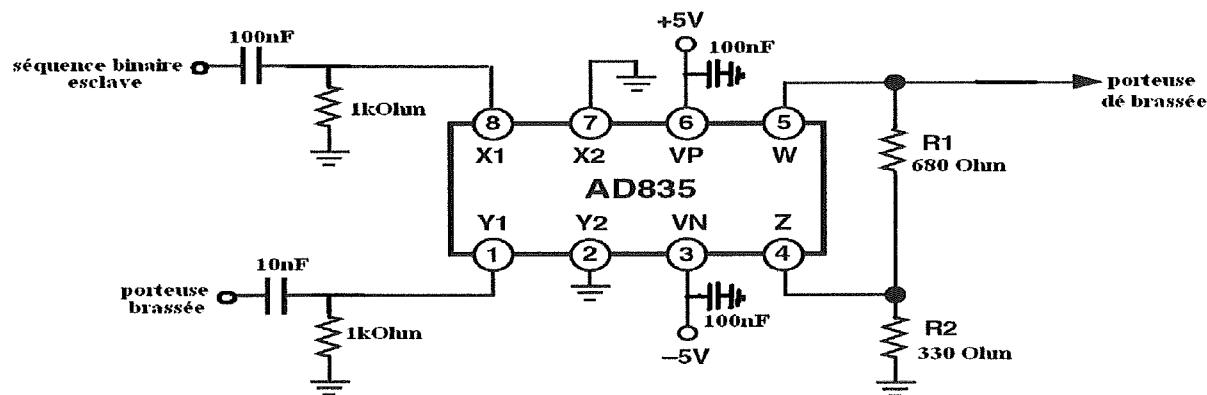

- Schéma électrique

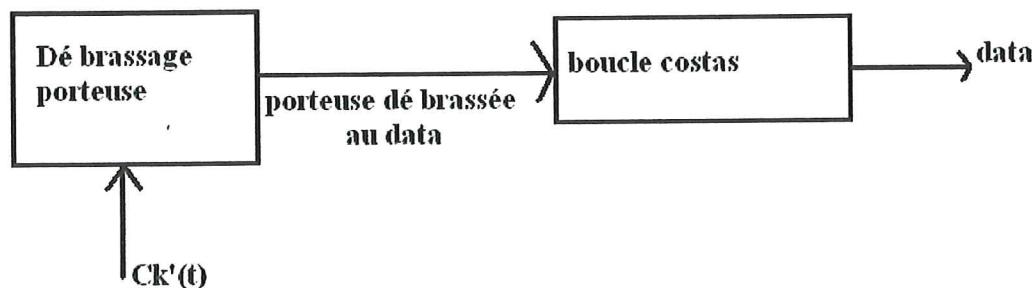

## 2.5.2) Porteuse dé brassée

- Rôle : Le but de notre carte didactique est de permettre la compréhension d'une porteuse brassée et dé brassée. De ce fait, la porteuse brassée précédemment réalisée sera dé brassée pour récupérer la porteuse seule.

Pour réaliser ce dé brassage, on multiplie la porteuse brassée par sa séquence code  $C'k(t)$  exactement en phase avec la séquence code  $Ck(t)$ .

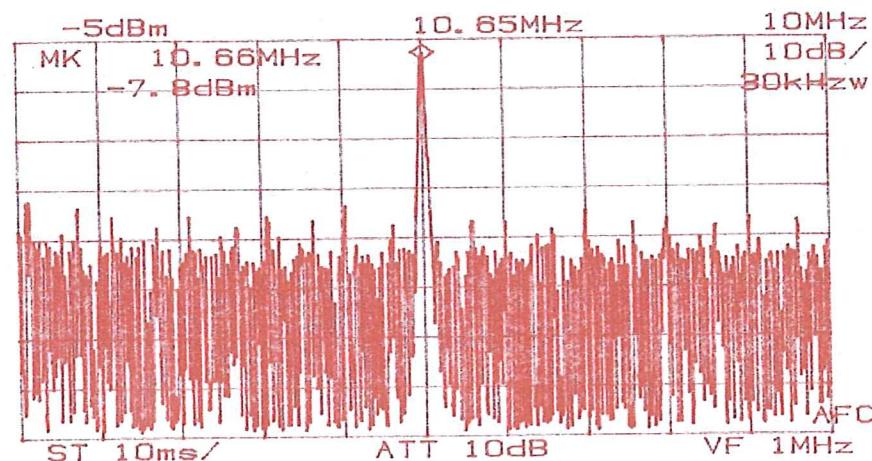

En effet, pour ne récupérer que la fréquence porteuse du signal,  $C'k(t)$  doit être égale à  $Ck(t)$  pour retrouver sa puissance moyenne dans une seule raie en représentation fréquentielle. (Voir courbe)

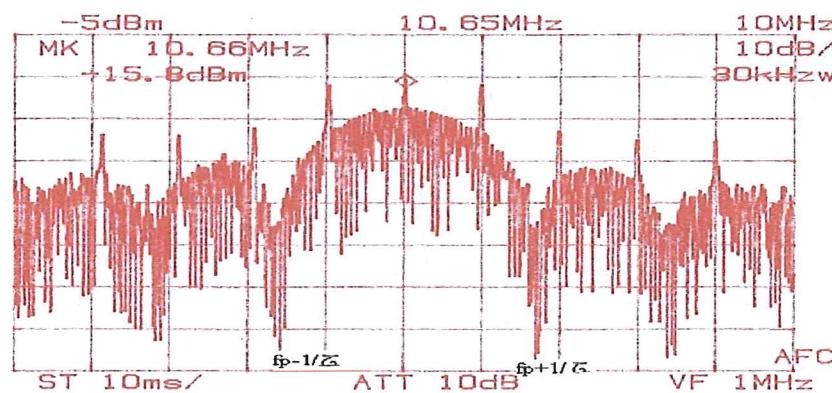

Lorsque l'on joue sur le retard ( $to$ ) entre les deux séquences, il se forme un lobe principal de largeur de bande  $2/to$  où  $-T_{code} < to < T_{code}$ . Ce lobe et la raie centrale porte la puissance moyenne de la porteuse en sortie de la voie de dé brassage. (Voir courbe)

On observe des raies périodiques à 1 Mhz autour de la fréquence de la porteuse du à  $D_{code}$  et du fait que l'on n'obtient pas une équiprobabilité entre l'apparition du « 1 » ( $P1$ ) et l'apparition du « 0 » ( $P0$ ). En effet, on obtient  $P0 = 7/15$  et  $P1 = 8/15$ .

De plus, on observe quinze raies périodiques entre la fréquence porteuse et la raie périodique à 1 Mhz. Cette écart de fréquence entre ces deux raies principales est de 66 kHz c'est-à-dire égal à  $1/15T_{code}$  car  $T = 15T_{code}$ . Ces raies sont dues au fait que l'on utilise une séquence binaire courte avec  $N = 4$  d'où  $2^N - 1 = 15$  bits. (Voir courbe)

Spectre porteuse débrassée à  $\tau = -T_c$

Spectre porteur débranlé à  $T=0$ Spectre porteur débranlé à  $T=T_p$

On peut expliquer ce résultat théoriquement :

On a  $s'(t) = a * \cos(wpt) * Ck(t) * C'k(t-\tau)$

Or la moyenne de  $(Ck(t) * C'k(t-\tau))$  est égal à l'équation d'auto corrélation.

Qui en réalité est matérialisée par  $a * \cos(wpt) * \text{signe}Ck(t) * \text{signe}C'k(t-\tau)$

On décrit le signal  $Ck * Ck'$  par sa moyenne et sa partie variable :

Or la moyenne du produit  $(Ck(t) * C'k(t-\tau))$  est l'auto corrélation.

La partie variable est une suite de changements de signes à chaque transition de  $Ck$ , à chaque transition apparaît un écart de durée  $\tau$ .

Calculons par Bennett la DSPM de cette suite d'impulsion de durée  $\tau$  et de probabilité  $P = 2^{N-1} / (2^N - 1)$  ( $2^{N-1}$  : nb de transitions dans une séquence).

Remplacer partout  $P_1$  par  $P$  (comme si symbole unique : l'impulsion de durée  $\tau$ ).

D'où d'après l'équation de Bennett :

$$S'xx(f) = 1/\tau * [P_1 |R(f)|^2] - 1/\tau * [P_1^2 * R(f)^2] + 1/\tau^2 * |P_1 * R(f)|^2 * \sum \delta(F - N/\tau)$$

$$S'xx(f) = 1/\tau * (A * \tau * \text{sinc} \pi f)^2 * (P_1 - P_1^2) + P_1^2 / \tau^2 * (A * \tau * \text{sinc} \pi f)^2 * \sum \delta(F - N/\tau)$$

$$S'xx(f) = (P_1 - P_1^2) * A^2 * \tau * (\text{sinc} \pi f)^2 + P_1^2 * A^2 * (\text{sinc} \pi f)^2 * \sum \delta(F - N/\tau)$$

Ainsi on observe une partie variable qui représente un peigne de Dirac et une partie constante en fonction de  $\tau$ .

Les Dirac disparaissent car coïncidant avec les "zéros" du sincar !

Le spectre est constitué d'une part :

Continuum ou DSPM en sincar au carré limité à + et  $-1/\tau$  dont l'amplitude est liée à  $(p - p^2)$ .

D'autre part :

Une moyenne (Dirac en zéro) d'aire égale à l'auto corrélation de  $C_k$

Le spectre de la porteuse dé brassée est obtenu par le théorème du changement de fréquence.

Soit une porteuse en  $+$  - fp accompagnée du continuum dont l'étalement dépend de l'écart temporel  $\tau$

Les spectres enregistrés montrent parfaitement le mécanisme de dé brassage de porteuse.

Plus  $\tau$  décroît plus le continu s'étale en perdant son aire donc sa puissance pendant que la porteuse dont l'amplitude est l'auto corrélation monte pour atteindre enfin la puissance initiale

La puissance de la porteuse dé brassée est celle de la porteuse initiale donc  $a^2/2$  en  $V^2$ .

Dans tous les cas de la puissance totale Dirac plus continuum de fréquence est  $a^2/2$  en  $V^2$ . C'est pour cela que lorsque l'on joue sur le retard  $\tau$ , la densité spectrale de la porteuse débrassée est différente. Ainsi, lorsque  $\tau = 0$ , la partie variable devient nulle et la moyenne est égale à une constante. C'est pour cela que l'on retrouve que la porteuse débrassée à la fréquence  $f_p$ .

## - Schéma électrique

### 3) – Schéma final

SVP joindre les flèches E et S

## CONCLUSION

A travers ce projet, on a pu ainsi comprendre le fonctionnement de la transmission d'information par CDMA. Cette carte didactique qui a pour but pédagogique va permettre aux élèves de mieux assimiler et comprendre le fonctionnement de ce mode de transmission.

Les résultats du projet sont positifs, nous avons constitué une carte qui fonctionne et qui explique le CDMA avec le principe d'étalement spectrale et de la corrélation pour la récupération de la porteuse. Ce projet nous aura permis de démystifier les mécanismes de brassage et dé brassage de porteuse .Et aussi de mieux comprendre les outils théoriques concernant la description spectrale

Avec plus de temps, nous aurions pu mettre en place une maquette finale composée des données data et de leurs récupérations en fin de transmission, ainsi que plusieurs données codées avec la récupération de chacune (voir principe de l'accès multiple avec code).

Pour réaliser cette carte le principal problème que l'on a pu rencontrer était d'ordre électromagnétique du fait des plans de masse de plusieurs plaques qui étaient mal reliées Pour ce faire nous avons du réaliser une seule plaque pour éviter d'avoir des interférences. Une fois ce problème résolu, les différentes manipulations que nous avons réalisées furent moins perturbées par ce phénomène. Ainsi, on a obtenu des courbes exploitables et avoir les résultats que l'on escomptait.

Ce projet nous aura permis d'apprendre à concevoir une carte électronique à l'aide de nos connaissances et des documentations. En conclusion, en électronique il n'y a rien à inventer mais juste à utiliser ses connaissances pour concevoir ce que l'on veut obtenir.

## ANNEXES

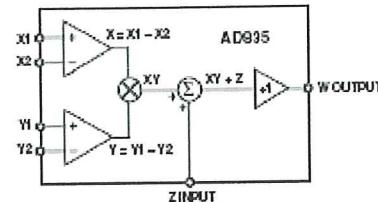

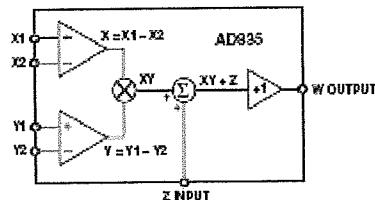

ANNEXE 1 : Multiplieur AD835

ANNEXE 2 : Ou exclusif 74HC86N

ANNEXE 3 : séquenceurs 74HC164

ANNEXE 4 : VCO 74HC4046N

ANNEXE 5 : INVERSEUR 74HCT04N

## ANNEXE 1 : Multiplieur AD835

## FEATURES

Simple: Basic Function is  $W = XY + Z$

Complete: Minimal External Components Required

Very Fast: Settles to 0.1% of FS in 20 ns

DC-Coupled Voltage Output Simplifies Use

High Differential Input Impedance X, Y, and Z Inputs

Low Multiplier Noise: 50 nV/Hz

## APPLICATIONS

Very Fast Multiplication, Division, Squaring

Wideband Modulation and Demodulation

Phase Detection and Measurement

Sinusoidal Frequency Doubling

Video Gain Control and Keying

Voltage Controlled Amplifiers and Filters

## PRODUCT DESCRIPTION

The AD835 is a complete four-quadrant voltage output analog multiplier, fabricated on an advanced dielectrically isolated complementary bipolar process. It generates the linear product of its X and Y voltage inputs with a 3 dB output bandwidth of 250 MHz (a small signal rise time of 1 ns). Full scale (-1 V to +1 V) rise to fall times are 2.5 ns (with the standard  $R_L$  of 150  $\Omega$ ), and the settling time to 0.1% under the same conditions is typically 20 ns. Its differential multiplication inputs (X, Y) and its summing input (Z) are at high impedance. The low impedance output voltage (W) can provide up to  $\pm 2.5$  V and drive loads as low as 25  $\Omega$ . Normal operation is from  $\pm 5$  V supplies.

Though providing state-of-the-art speed, the AD835 is simple to use and versatile. For example, as well as permitting the addition of a signal at the output, the Z input provides the means to operate the AD835 with voltage gains up to about  $\times 10$ . In this capacity, the very low product noise of this multiplier (50 nV/Hz) makes it much more useful than earlier products.

The AD835 is available in an 8-lead PDIP package (N) and an 8-lead SOIC package (R) and is specified to operate over the  $-40^\circ\text{C}$  to  $+85^\circ\text{C}$  industrial temperature range.

## FUNCTIONAL BLOCK DIAGRAM

## PRODUCT HIGHLIGHTS

1. The AD835 is the first monolithic 250 MHz four quadrant voltage output multiplier.

2. Minimal external components are required to apply the AD835 to a variety of signal processing applications.

3. High input impedances (100 k $\Omega$ /2 pF) make signal source loading negligible.

4. High output current capability allows low impedance loads to be driven.

5. State of the art noise levels achieved through careful device optimization and the use of a special low noise band gap voltage reference.

6. Designed to be easy to use and cost effective in applications which formerly required the use of hybrid or board level solutions.

## REV.B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 [www.analog.com](http://www.analog.com)

Fax: 781/326-8709 © 2003 Analog Devices, Inc. All rights reserved.

## AD835

## PRODUCT DESCRIPTION

The AD835 is a four-quadrant voltage output analog multiplier, fabricated on an advanced dielectrically isolated complementary bipolar process. In its basic mode, it provides the linear product of its X and Y voltage inputs. In this mode, the -3 dB output voltage bandwidth is 250 MHz (a small signal rise time of 1 ns). Full scale (-1 V to +1 V) rise to fall times are 2.5 ns (with the standard  $R_L$  of 150  $\Omega$ ) and the settling time to 0.1% under the same conditions is typically 20 ns.

As in earlier multipliers from Analog Devices, a unique summing feature is provided at the Z input. As well as providing independent ground references for input and output and enhanced versatility, this feature allows the AD835 to operate with voltage gain. Its X-, Y-, and Z-input voltages are all nominally  $\pm 1$  V FS, with an overrange of at least 20%. The inputs are fully differential at high impedance (100 k $\Omega$ /2 pF) and provide a 70 dB CMRR ( $f \leq 1$  MHz).

The low impedance output is capable of driving loads as small as 25  $\Omega$ . The peak output can be as large as  $\pm 2.2$  V minimum for  $R_L = 150 \Omega$ , or  $\pm 2.0$  V minimum from  $R_L = 50 \Omega$ . The AD835 has much lower noise than the AD534 or AD734, making it attractive in low level signal-processing applications, for example, as a wideband gain-control element or modulator.

## Basic Theory

The multiplier is based on a classic form, having a translinear core, supported by three (X, Y, Z) linearized voltage-to-current converters, and the load driving output amplifier. The scaling voltage (the denominator U in the equations below) is provided by a band gap reference of novel design, optimized for ultralow noise. Figure 1 shows the functional block diagram.

In general terms, the AD835 provides the function

$$W = \frac{(X_1 - X_2)(Y_1 - Y_2)}{U} + Z \quad (1)$$

where the variables W, U, X, Y, and Z are all voltages. Connected as a simple multiplier, with  $X = X_1 - X_2$ ,  $Y = Y_1 - Y_2$ , and  $Z = 0$  and with a scale factor adjustment (see Figure 1), which sets  $U = 1$  V, the output can be expressed as

$$W = XY \quad (2)$$

Figure 1. Functional Block Diagram

Simplified representations of this sort, where all signals are presumed to be expressed in V, are used throughout this data sheet to avoid the needless use of less-intuitive subscripted variables (such as  $V_{X1}$ ). We can view all variables as being normalized to 1 V. For example, the input X can either be stated as being in the range -1 V to +1 V or simply -1 to +1. The latter representation

will be found to facilitate the development of new functions using the AD835. The explicit inclusion of the denominator, U, is also less helpful, as in the case of the AD835, if it is not an electrical input variable.

## Scaling Adjustment

The basic value of U in Equation 1 is nominally 1.05 V. Figure 2, which shows the basic multiplier connections, also shows how the effective value of U can be adjusted to have any lower voltage (usually 1 V) through the use of a resistive-divider between W (Pin 5) and Z (Pin 4). Using the general resistor values shown, we can rewrite Equation 1 as

$$W' = \frac{XY}{U} + kW + (1-k)Z \quad (3)$$

where Z is distinguished from the signal Z at Pin 4. It follows that

$$W' = \frac{XY}{(1-k)U} + Z' \quad (4)$$

In this way, we can modify the effective value of U to

$$U' = (1-k)U \quad (5)$$

without altering the scaling of the Z input. (This is to be expected since the only "ground reference" for the output is through the Z input.)

Thus, to set U' to 1 V, remembering that the basic value of U is 1.05 V, we need to choose R1 to have a nominal value of 20 times R2. The values shown here allow U' to be adjusted through the nominal range 0.95 V to 1.05 V. That is, R2 provides a 5% gain adjustment.

Note that in many applications, the exact gain of the multiplier may not be very important; in which case, this network may be omitted entirely, or R2 fixed at 100  $\Omega$ .

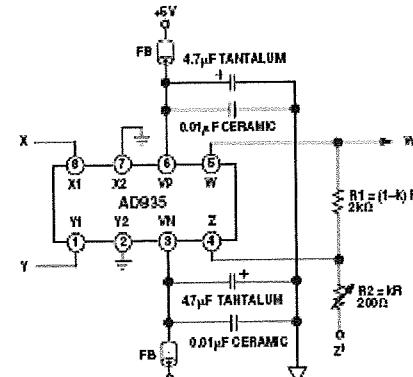

Figure 2. Multiplier Connections

## ANNEXE 2 : Ou exclusif 74HC86N

Philips Semiconductors

Product specification

Quad 2-input EXCLUSIVE-OR gate

74HC/HCT86

## PIN DESCRIPTION

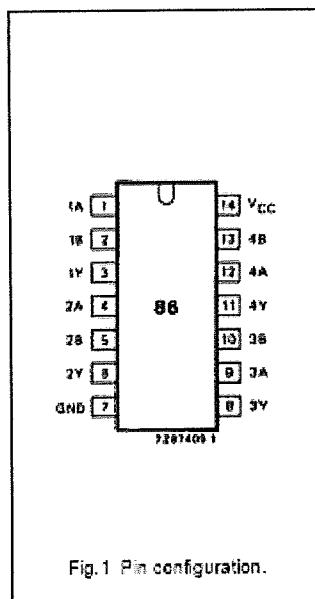

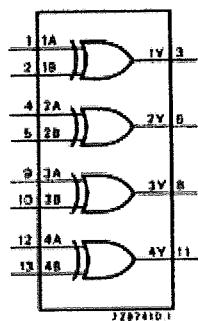

| PIN NO.      | SYMBOL          | NAME AND FUNCTION       |

|--------------|-----------------|-------------------------|

| 1, 4, 9, 12  | 1A to 4A        | data inputs             |

| 2, 5, 10, 13 | 1B to 4B        | data inputs             |

| 3, 6, 8, 11  | 1Y to 4Y        | data outputs            |

| 7            | GND             | ground (0 V)            |

| 14           | V <sub>cc</sub> | positive supply voltage |

Fig.1 Pin configuration.

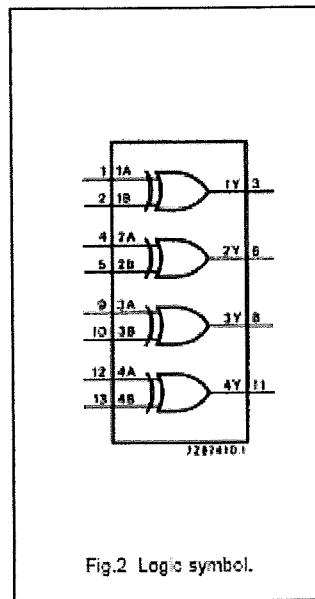

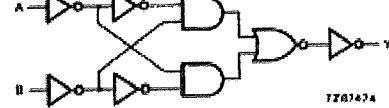

Fig.2 Logic symbol.

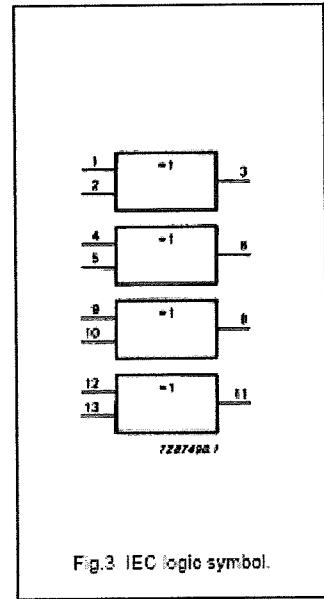

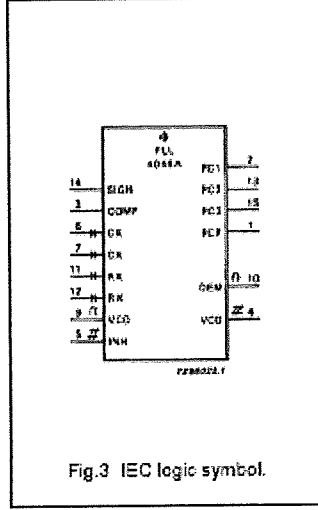

Fig.3 IEC logic symbol.

Philips Semiconductors

Product specification

## Quad 2-input EXCLUSIVE-OR gate

74HC/HCT86

Fig.4 Functional diagram.

Fig.5 Logic diagram (one gate).

## FUNCTION TABLE

| INPUTS |    | OUTPUTS |

|--------|----|---------|

| nA     | nB | nY      |

| L      | L  | L       |

| L      | H  | H       |

| H      | L  | H       |

| H      | H  | L       |

## Notes

1. H = HIGH voltage level

- L = LOW voltage level

December 1990

4

## ANNEXE 3 : séquenceurs 74HC164

**SGS-THOMSON**

MICROELECTRONICS

**M54HC164**

**M74HC164**

**8 BIT SIPO SHIFT REGISTER**

**■ HIGH SPEED**

$t_{PD} = 15 \text{ ns (TYP.)}$  AT  $V_{CC} = 5 \text{ V}$

**■ LOW POWER DISSIPATION**

$I_{CC} = 4 \mu\text{A (MAX.)}$  AT  $T_A = 25^\circ\text{C}$

**■ OUTPUT DRIVE CAPABILITY**

10 LSTTL LOADS

**■ BALANCED PROPAGATION DELAYS**

$t_{PLH} = t_{PHL}$

**■ SYMMETRICAL OUTPUT IMPEDANCE**

$|I_{OL}| = |I_{OH}| = 4 \text{ mA (MIN.)}$

**■ HIGH NOISE IMMUNITY**

$V_{NH4} = V_{NL4} = 28\% V_{CC} (\text{MIN.})$

**■ WIDE OPERATING VOLTAGE RANGE**

$V_{CC} (\text{OPR}) = 2 \text{ V TO } 6 \text{ V}$

**■ PIN AND FUNCTION COMPATIBLE**

WITH 5474LS164

**B1R**

(Plastic Package)

**F1R**

(Ceramic Package)

**M1R**

(Micro Package)

**C1R**

(Chip Carrier)

**ORDER CODES :**

M54HC164F1R M74HC164M1R

M74HC164S1R M74HC164C1R

**PIN CONNECTIONS (top view)**

DA 14

NC 13

QB 12

NC 11

QC 10

NC 9

NC 8

GND 15

NC 16

NC 17

NC 18

NC 19

NC 20

NC 21

NC = No Internal Connection

**DESCRIPTION**

The M5474HC164 is a high speed CMOS 8 BIT SIPO SHIFT REGISTER fabricated in silicon gate CMOS technology. It has the same high speed performance of LSTTL combined with true CMOS low power consumption.

The HC164 is an 8 bit shift register with serial data entry and an output from each of the eight stages. Data is entered serially through one of two inputs (A or B); either of these inputs can be used as an active high enable for data entry through the other input. An unused input must be high, or both inputs connected together. Each low-to-high transition on the clock input shifts data one place to the right and enters into QA, the logic NAND of the two data inputs (A + B), the data that existed before the rising clock edge. A low level on the clear input overrides all other inputs and clears the register asynchronously, forcing all Q outputs low.

All inputs are equipped with protection circuits against static discharge and transient excess voltage.

## ANNEXE 4 : VCO 74HC4046N

Philips Semiconductors

Product specification

## Phase-locked-loop with VCO

## 74HC/HCT4046A

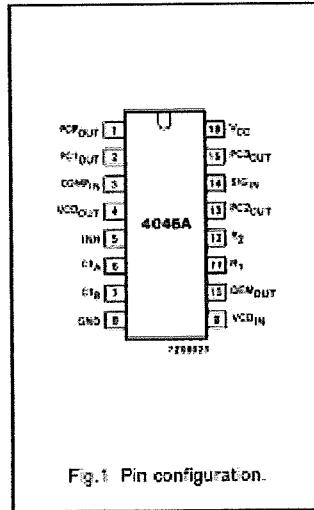

## PIN DESCRIPTION

| PIN NO. | SYMBOL             | NAME AND FUNCTION             |

|---------|--------------------|-------------------------------|

| 1       | PCP <sub>OUT</sub> | phase comparator pulse output |

| 2       | PC1 <sub>OUT</sub> | phase comparator 1 output     |

| 3       | COMP <sub>IN</sub> | comparator input              |

| 4       | VCO <sub>OUT</sub> | VCO output                    |

| 5       | INH                | inhibit input                 |

| 6       | C <sub>1A</sub>    | capacitor C1 connection A     |

| 7       | C <sub>1B</sub>    | capacitor C1 connection B     |

| 8       | GND                | ground (0 V)                  |

| 9       | VCO <sub>IN</sub>  | VCO input                     |

| 10      | DEM <sub>OUT</sub> | demodulator output            |

| 11      | R <sub>1</sub>     | resistor R1 connection        |

| 12      | R <sub>2</sub>     | resistor R2 connection        |

| 13      | PC2 <sub>OUT</sub> | phase comparator 2 output     |

| 14      | SIG <sub>IN</sub>  | signal input                  |

| 15      | PC3 <sub>OUT</sub> | phase comparator 3 output     |

| 16      | V <sub>CC</sub>    | positive supply voltage       |

Fig.1 Pin configuration.

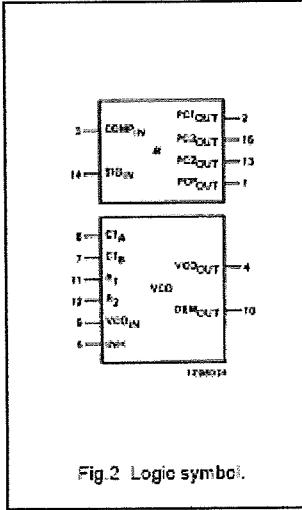

Fig.2 Logic symbol.

Fig.3 IEC logic symbol.

## ANNEXE 5 : INVERSEUR 74HCT04N

Philips Semiconductors

Product specification

Hex inverter

74HC04; 74HCT04

## ORDERING INFORMATION

| TYPE NUMBER | PACKAGE           |      |          |          |          |

|-------------|-------------------|------|----------|----------|----------|

|             | TEMPERATURE RANGE | PINS | PACKAGE  | MATERIAL | CODE     |

| 74HC04N     | -40 to +125 °C    | 14   | DIP14    | plastic  | SOT27-1  |

| 74HCT04N    | -40 to +125 °C    | 14   | DIP14    | plastic  | SOT27-1  |

| 74HC04D     | -40 to +125 °C    | 14   | SO14     | plastic  | SOT108-1 |

| 74HCT04D    | -40 to +125 °C    | 14   | SO14     | plastic  | SOT108-1 |

| 74HC04DB    | -40 to +125 °C    | 14   | SSOP14   | plastic  | SOT337-1 |

| 74HCT04DB   | -40 to +125 °C    | 14   | SSOP14   | plastic  | SOT337-1 |

| 74HC04PW    | -40 to +125 °C    | 14   | TSSOP14  | plastic  | SOT402-1 |

| 74HCT04PW   | -40 to +125 °C    | 14   | TSSOP14  | plastic  | SOT402-1 |

| 74HC04BQ    | -40 to +125 °C    | 14   | DHVQFN14 | plastic  | SOT762-1 |

| 74HCT04BQ   | -40 to +125 °C    | 14   | DHVQFN14 | plastic  | SOT762-1 |

## PINNING

| PIN | SYMBOL          | DESCRIPTION    |

|-----|-----------------|----------------|

| 1   | 1A              | data input     |

| 2   | 1Y              | data output    |

| 3   | 2A              | data input     |

| 4   | 2Y              | data output    |

| 5   | 3A              | data input     |

| 6   | 3Y              | data output    |

| 7   | GND             | ground (0 V)   |

| 8   | 4Y              | data output    |

| 9   | 4A              | data input     |

| 10  | 5Y              | data output    |

| 11  | 5A              | data input     |

| 12  | 6Y              | data output    |

| 13  | 6A              | data input     |

| 14  | V <sub>CC</sub> | supply voltage |

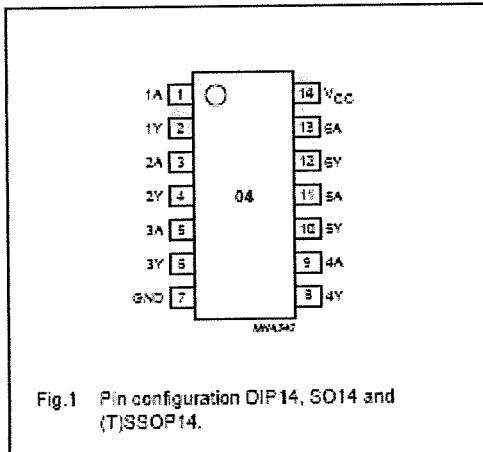

Fig.1 Pin configuration DIP14, SO14 and (T)SSOP14.